# ADM16F03A1 数字信号处理器

ADM16F03A1QP48Q、ADM16F03A1QN48Q

# 数据手册

编号: JXDZ3.590.031SJSC

# 湖南进芯电子科技有限公司

2024年07月 V1.4

# 目 次

| 1  | . 广面专生              | I    |

|----|---------------------|------|

| 2. | 型号命名规则              | 2    |

| 3. | 系统概述                | 3    |

| 4. | 引脚排布与说明             | 4    |

| 5. | 内存映射                | 6    |

|    | 5.1 存储空间映射          | 6    |

|    | 5.2 外设空间映射          | 7    |

| 6. | 内核说明                | 8    |

|    | 6.1 内核结构原理          | 8    |

|    | 6.2 系统寄存器           | 10   |

|    | 6.2.1 系统状态寄存器       | 10   |

|    | 6.2.2 系统控制寄存器       | 12   |

| 7  | 存储系统                | 15   |

|    | 7.1 片上存储器           | 15   |

|    | 7.2 双存取 RAM (DARAM) | 15   |

|    | 7.3 单存取 RAM (SARAM) | 15   |

|    | 7.4 闪存 Flash        | 15   |

|    | 7.4.1 Flash 说明      | 15   |

|    | 7.4.2 唯一 ID         | 16   |

|    | 7.4.3 Cache 说明      | 16   |

| 8  | 时钟系统                | 19   |

|    | 8.1 PLL 时钟模块        | 19   |

|    | 8.2 PLL 时钟模块控制寄存器   | 20   |

|    | 8.3 片内高精度 OSC       | 21   |

| 9  | 中断系统                | 22   |

|    | 9.1 中断系统结构          | 22   |

|    | 9.2 CPU 中断寄存器       | 25   |

|    | 9.3 外设中断控制寄存器       | 27   |

|    | 9.4 外设中断控制寄存器       | 32   |

| 1( | 0 看门狗               | . 34 |

|    | 10.1 看门狗模块结构框图      | 34   |

| ADM16F03A1 Digital Signal Processor | V1.4 |

|-------------------------------------|------|

| 10.2 看门狗控制寄存器                       | 35   |

| 11 硬件加速单元                           | 38   |

| 11.1 硬件加速单元功能介绍                     | 38   |

| 11.2 硬件加速单元各模块详细说明                  | 39   |

| 11.2.1 开平方根模块                       | 39   |

| 11.2.2 除法器模块                        | 41   |

| 11.2.3 Park 运算模块                    | 44   |

| 11.2.4 乘法移位器模块                      | 46   |

| 11.2.5 Cordic 模块                    | 50   |

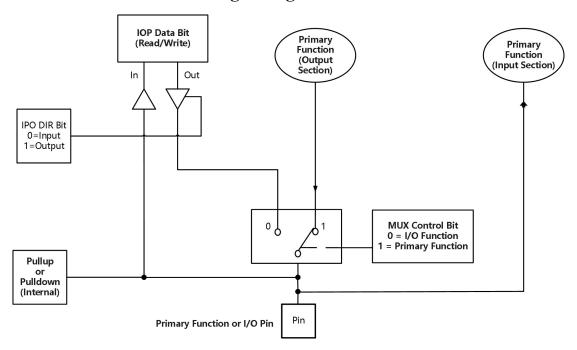

| 12 数字 I/O 口与引脚复用功能                  | 54   |

| 12.1 数字 I/O 口与引脚复用功能描述              | 54   |

| 12.1.1 复用 I/O 引脚描述                  | 54   |

| 12.2 数字 I/O 控制寄存器                   | 55   |

| 12.2.1 I/O 端口复用控制寄存器 PORTA,PORTB    | 55   |

| 12.2.2 I/O 端口复用控制寄存器 PORTC,PORTD    | 58   |

| 12.2.3 I/O 端口复用控制寄存器 PORTE, PORTF   | 59   |

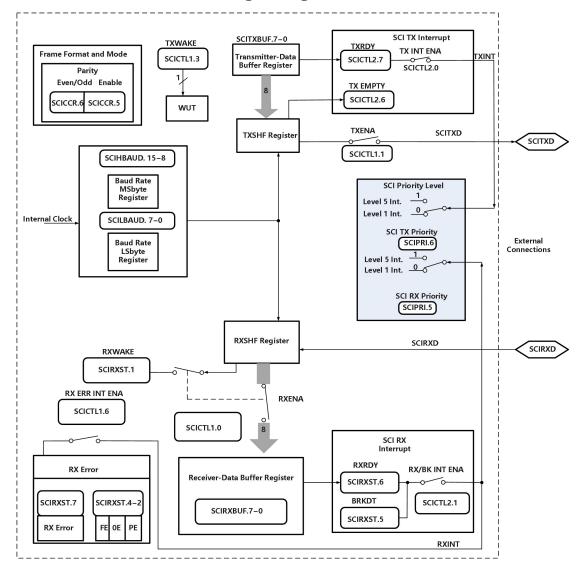

| 13 串行通信接口 SCI                       | 62   |

| 13.1 串行通信接口 SCI 功能简介                | 62   |

| 13.2 SCI 寄存器                        | 64   |

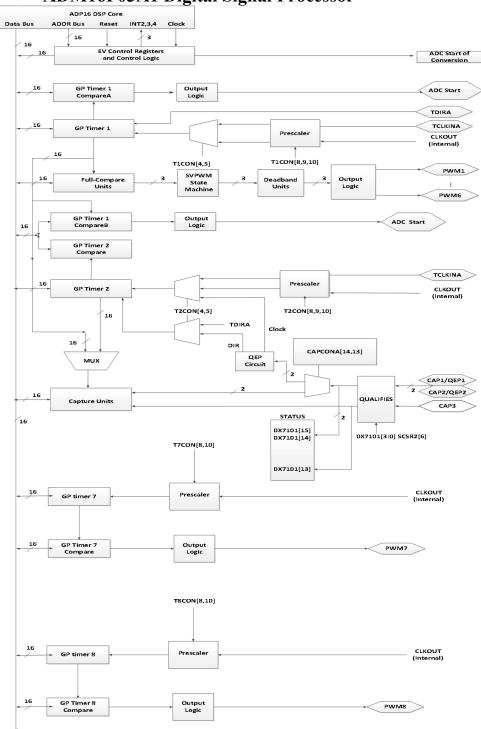

| 14 事件管理器模块 EM1                      | 70   |

| 14.1 事件管理器模块 EM1 简介                 | 70   |

| 14.2 事件管理器模块 EM1 中断                 | 71   |

| 14.2.1 事件管理器模块 EM1 中断组              | 71   |

| 14.2.2 事件管理器模块(EM1)中断控制寄存器          | 72   |

| 14.3 事件管理器 EM1 通用定时器                | 74   |

| 14.3.1 事件管理器 EM1 通用定时器控制寄存器         | 75   |

| 14.4 事件管理器模块 EM1 全功能比较单元            | 80   |

| 14.4.1 事件管理器模块 EM1 全功能比较控制寄存器       | 80   |

| 14.5 事件管理器模块 EM1 脉宽调制电路             | 82   |

| 14.5.1 PWM 特性                       | 82   |

| 14.5.2 PWM 相关寄存器                    | 83   |

| 14.6 事件管理器模块 (EM1) 捕获单元             | 84   |

| 14.6.1 事件管理器模块(EM1)捕获单元控制寄存器        | 84   |

| 14.7 正交编码脉冲(OFP) 电路                 | 86   |

| ADM16F03A1 Digital Signal Processor | V1.4 |

|-------------------------------------|------|

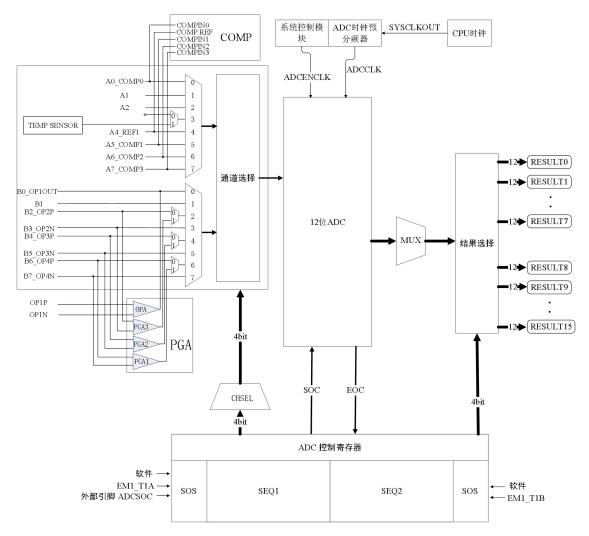

| 15 模数转换器 ADC                        | 87   |

| 15.1 ADC 的特性                        | 87   |

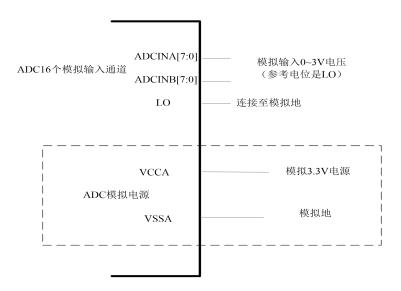

| 15.2 ADC 模块概述                       | 88   |

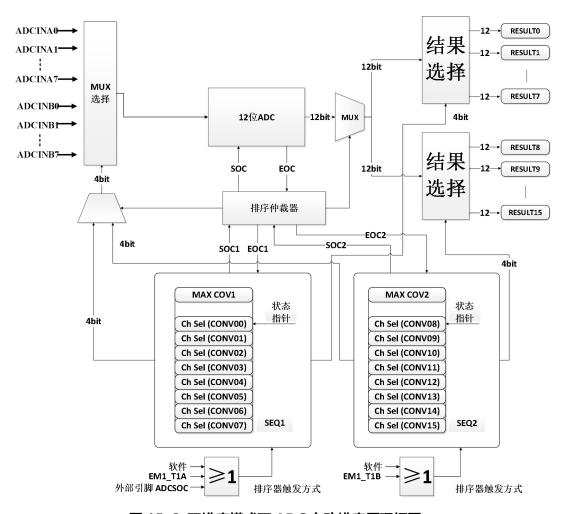

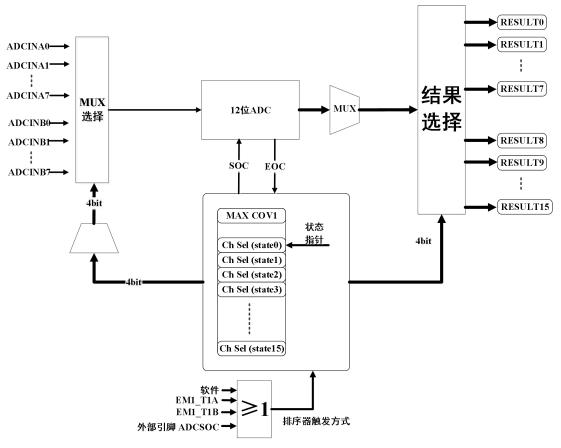

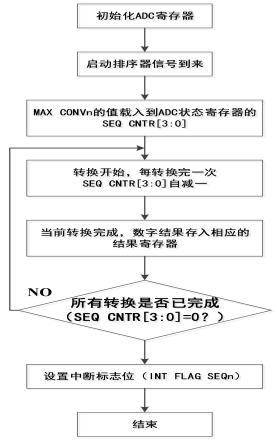

| 15.3 自动排序器                          | 90   |

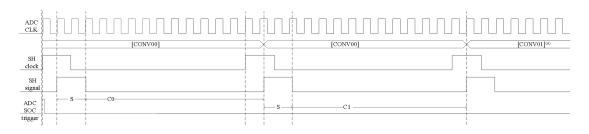

| 15.3.1 顺序采样模式                       | 93   |

| 15.3.2 不中断的自动排序模式                   | 94   |

| 15.3.3 排序器的启/停工作模式                  | 97   |

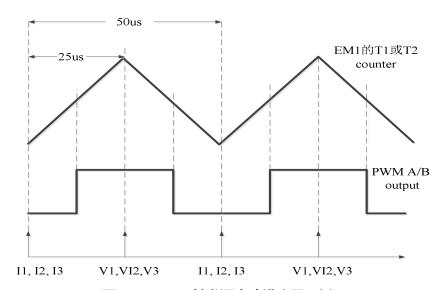

| 15.3.4 输入触发源                        | 99   |

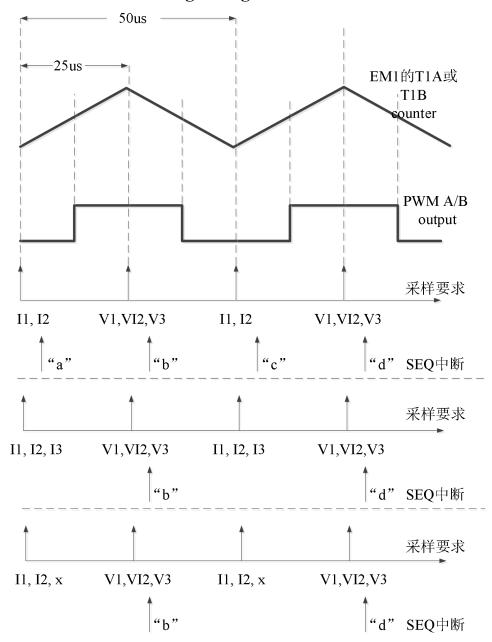

| 15.3.5 排序转换期间的中断操作                  | 99   |

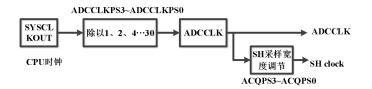

| 15.4 ADC 时钟预分频                      | 102  |

| 15.5 ADC 校准                         | 103  |

| 15.6 片内温度传感器                        | 103  |

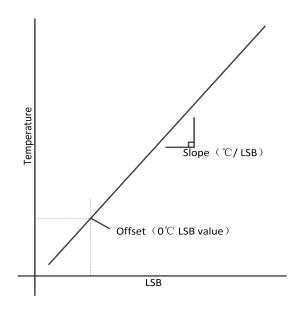

| 15.6.1 温度传感器传递函数                    | 103  |

| 15.7 ADC 寄存器概述                      | 105  |

| 16 运放与复用数字 IO 输入                    | 115  |

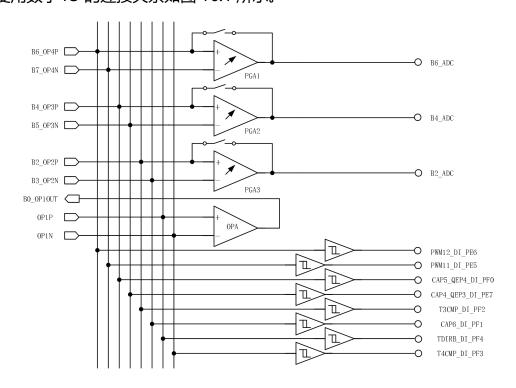

| 16.1 运放与复用数字 IO 输入说明                | 115  |

| 16.2 运放与复用数字 IO 输入寄存器               | 117  |

| 16.2.1 通道对应的配置寄 <del>存器</del>       | 117  |

| 16.2.2 OPA 与 PGA 配置寄存器              | 118  |

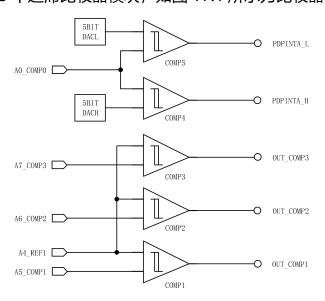

| 17 电压比较器                            | 121  |

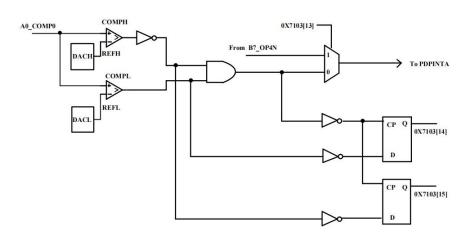

| 17.1 电压比较器说明                        | 121  |

| 17.1.1 内阈值电压比较器                     | 121  |

| 17.1.2 外阈值组电压比较器                    | 122  |

| 17.1.3 电压比较器控制寄存器                   | 123  |

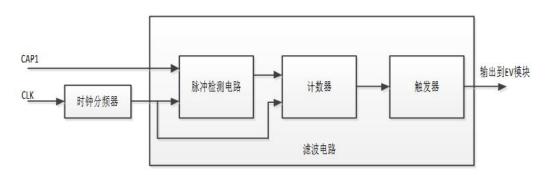

| 18 数字延时滤波                           | 128  |

| 18.1 数字延时滤波模块结构                     | 128  |

| 18.2 数字延时滤波模块寄存器说明                  | 129  |

| 18.2.1 数字延时滤波控制寄存器                  |      |

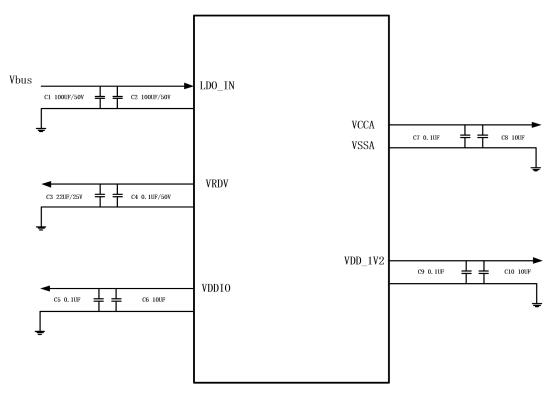

| 19 供电                               | 131  |

| 19.1 片上 LDO 电源管理                    |      |

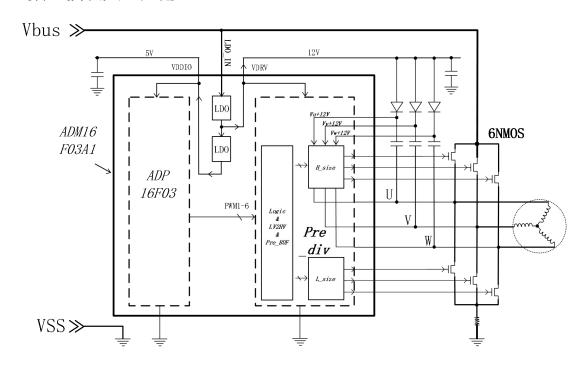

| 20 栅极驱动模块                           | 133  |

| 20.1 预驱模块典型应用                       | 133  |

| 21 电气参数                             | 134  |

| 21.1 建议的运行条件                        | 134  |

| ▲ 进                                                                                   | V1.4                    |

|---------------------------------------------------------------------------------------|-------------------------|

| 21.2 建议运行温度范围内的电气特性                                                                   | 134                     |

| 21.3 减少流耗                                                                             | 134                     |

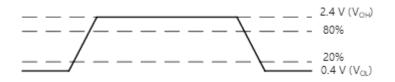

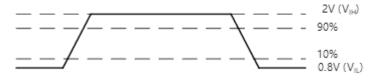

| 21.4 信号转换电平                                                                           | 135                     |

| 21.5 时序参数符号                                                                           | 136                     |

| 21.6 定时参数的通用注释                                                                        | 136                     |

| 21.7 12 位模数转换器(ADC)                                                                   | 136                     |

| 21.8 ADC 建议运行条件                                                                       | 136                     |

| 21.9 ADC 工作频率设定                                                                       | 137                     |

| 21.10 推荐工况下的 ADC 电气特性                                                                 | 137                     |

| 21.11 预驱模块参数                                                                          | 138                     |

| 21.11.1 最大额定值                                                                         | 138                     |

| 21.11.2 推荐工作条件(无特别说明情况下,测试条件为 $T_A$ =25℃)                                             | 138                     |

| 21.11.3 静态电气参数                                                                        | 139                     |

| 21.11.4 动态电气参数(无特别说明情况下, $V_{BIAS}$ = $V_{DRV}$ = $V_{B}$ =15 $V$ , $C_{L}$ =1000 $p$ | F, T <sub>A</sub> =25℃) |

|                                                                                       | 140                     |

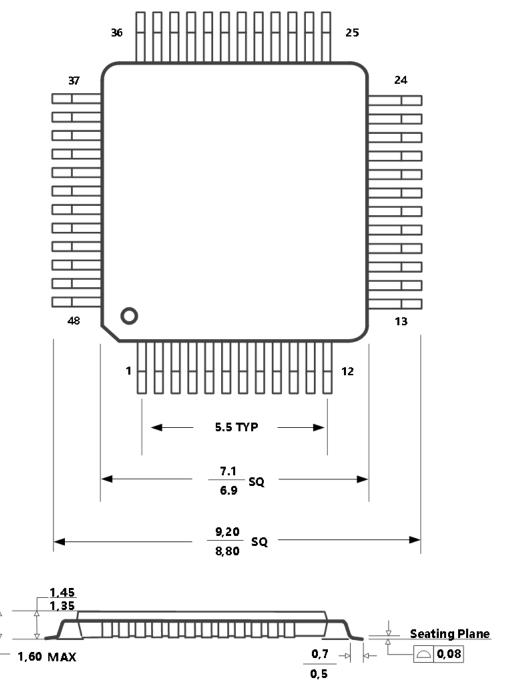

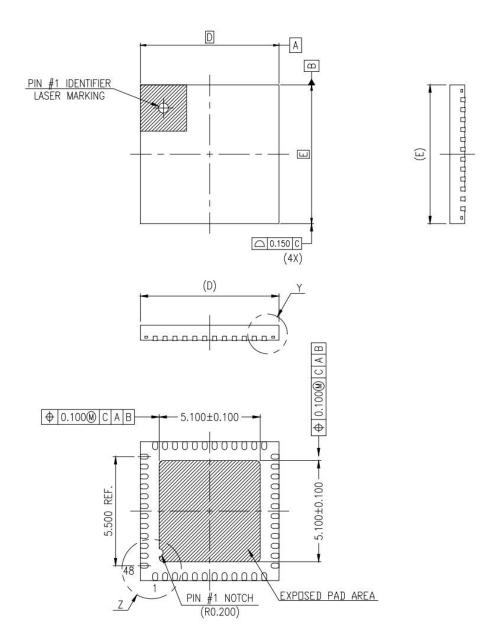

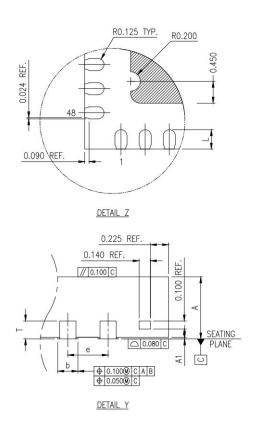

| 22 机械数据                                                                               | 141                     |

| 23. 重要注音重质及吉阳                                                                         | 144                     |

# 图清单

| 图 3. 1   | ADM16F03A1 系统框图                           | 3   |

|----------|-------------------------------------------|-----|

| 图 4. 1   | ADM16F03A1_LQFP48 (左) 与 VQFN48 (右) 封装引脚排布 | 4   |

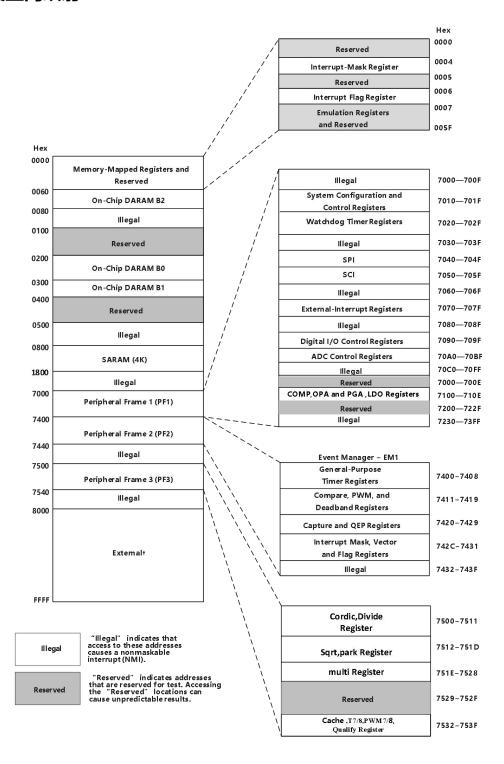

| 图 5. 1   | ADM16F03A1 存储空间映射                         | 6   |

| 图 5. 2   | ADM16F03A1 外设空间映射                         | 7   |

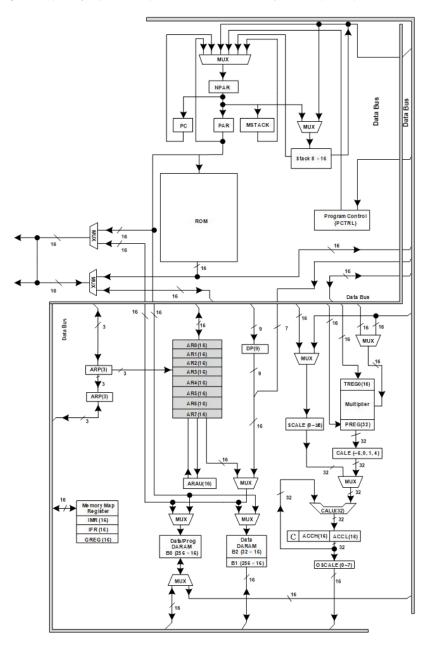

| 图 6. 1   | CPU 功能模块框图                                | 8   |

| 图 7. 1   | cache 配置流程图                               | 17  |

| 图 8. 1   | PLL 时钟模块功能框图                              | 19  |

| 图 8. 2   | PLL 时钟旁路控制信号时序                            | 19  |

| 图 9. 1   | PIE 中断硬件结构框架                              | 23  |

| 图 10. 1  | 看门狗功能框图                                   | 35  |

| 图 12. 1  | I/O 复用控制框图                                | 55  |

| 图 13. 1  | SCI 功能框图                                  | 64  |

| 图 14. 1  | 事件管理器模块 EM1 功能框图                          | 71  |

| 图 15. 1  | ADC 系统结构框图                                | 89  |

| 图 15. 2  | ADC 电源引脚连接示例                              | 90  |

| 图 15. 3  | 双排序模式下 ADC 自动排序原理框图                       | 91  |

| 图 15. 4  | 级联模式下 ADC 自动排序原理框图                        | 92  |

| 图 15. 5  | 顺序采样模式的时序                                 | 93  |

| 图 15. 6  | 不间断的自动排序模式 ADC 转换流程图                      | 96  |

| 图 15. 7  | EM1 触发源启动排序器示例                            | 98  |

| 图 15.8   | 多次排序转换之间的中断操作                             | 102 |

| 图 15. 9  | ADC 时钟预分频                                 | 103 |

| 图 15. 10 | 0 温度传感器传递函数                               | 104 |

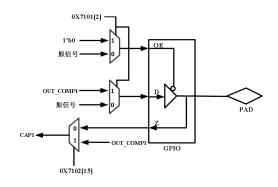

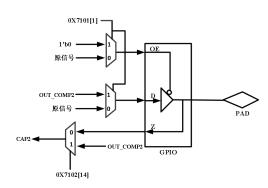

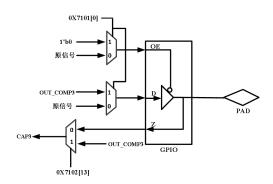

|          | 运放与数字 I/O 复用连接                            |     |

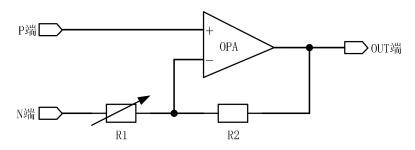

| 图 16. 2  | PGA 等效电路                                  | 116 |

| 图 17. 1  | 比较器模块内部框架图                                | 121 |

|          | 内阈值组电压比较器框图                               |     |

| 图 17. 3  | 外阈值组电压比较器组框图                              | 123 |

| 图 18. 1  | CAP1 数字延时滤波示意图                            | 128 |

| 图 19. 1  | 芯片供电连接参考图示                                | 132 |

|  | ADM16F03A1 | <b>Digital</b> | <b>Signal</b> | <b>Processor</b> |

|--|------------|----------------|---------------|------------------|

|--|------------|----------------|---------------|------------------|

| <b>T</b> 71 | 1 1 |

|-------------|-----|

| v           | - 4 |

| 图 20. 1 |

|---------|

| 图 21. 1 |

| 图 21. 2 |

| 图 22. 1 |

|         |

|         |

|         |

# 表清单

| 表 4. 1  | ADM16F03A1 芯片引脚功能定义            |     |  |  |

|---------|--------------------------------|-----|--|--|

| 表 6. 1  | CPU 内部硬件模块说明                   |     |  |  |

| 表 8. 1  | SCSR1 寄存器配置 PLL 倍频系数表          | 20  |  |  |

| 表 8. 2  | OSC 的指标参数                      | 21  |  |  |

| 表 9. 1  | 中断源优先级与中断向量表                   | 24  |  |  |

| 表 10. 1 | WD 溢出时间选择                      | 37  |  |  |

| 表 12. 1 | 数字 I/O 模块控制寄存器                 | 55  |  |  |

| 表 14. 1 | 针对 EM1 模块和信号名称                 | 70  |  |  |

| 表 15. 1 | 不同工作模式 SEQ1 和 SEQ2 比较          | 93  |  |  |

| 表 15. 2 | 示例 2 中 CHSELSEQn 寄存器写入值        | 95  |  |  |

| 表 15. 3 | CHSELSEQ n 设定值(MAX_CONV1 设为 2) | 98  |  |  |

| 表 15. 4 | 第二次自动转换会话后的值                   | 98  |  |  |

| 表 15. 5 | 输入触发源                          | 99  |  |  |

| 表 15.6  | CALIBRATION 校准寄存器—70B8h        | 103 |  |  |

| 表 15. 7 | 温度传感器特性                        | 104 |  |  |

| 表 15.8  | ADC 相关寄存器列表                    | 105 |  |  |

| 表 16. 1 | PGA 内阻 R1 与 R2 数值              | 117 |  |  |

| 表 16. 2 | PGA 放大倍数配置关系                   | 119 |  |  |

| 表 17. 1 | COMP 迟滞电压配置关系                  | 127 |  |  |

| 表 18. 1 | 延时滤波时间参考配置表                    | 128 |  |  |

| 表 21. 1 | ADC 建议运行条件                     | 136 |  |  |

| 表 21. 2 | ADC 工作频率范围                     | 137 |  |  |

| 表 21 3  | 推荐工况下的 ADC 由气特性                | 137 |  |  |

### 1. 产品特性

### 单电源供电

- $-4.5V \sim 40V$

- 集成 LDO(预驱 12V, 内核 1.2V, 数字 IO 口 5V, 模拟 3V)

### ・高性能 16 位定点 DSP 内核

- -主频最高 150MHz

- -哈佛(Harvard)总线结构

- -快速中断响应和处理

### · 片内存储器资源

- 4K x 16 位 SARAM

- (256+256+32) x 16 位 DARAM

- 32K x 16 位 Flash

### ・运算加速单元

- -除法、开方

- -反正切

- 帕克变换

- 32 位乘加及移位

### · 17 个通用 I/O 引脚

#### ・事件管理器 EM1

- 4 个 16 位定时/计数器

- 8 路 PWM 输出

(PWM1~6 构成 3 组互补输出,

- PWM7/8 独立输出)

- 1组正交编码单元

- 3 个捕获单元(CAP1/2/3)

- 可配置 PWM 周期内中断产生和 ADC 采样触发时刻

### •集成三相高、低侧半桥驱动电路

- -六路 NMOS Pre-Driver

- -栅极驱动电路高侧浮动绝对电压可达 200V

- -驱动能力 IO+/ IO-:+1.2A/-2.0A @VDRV=12V, VBS=12V

#### ADC

- 12 位, 转换速率 1MSPS

- 16 通道,连接到片内温度传感器

- 通道排序器,可设置 ADC 采样通道序列

### • 运算放大器

- 1个 OP, 可用于母线电流信号调理

- 3 个 PGA, 可用于相电流信号调理

### ・电压比较器

- 3 个电压比较器,参考端共用, 可用于 BEMF 比较检测

- 2 个电压比较器,带参考电压 (DAC 产生),可用于保护

### 中断

- 2个外部中断

- 29 个由 PIE 设置的外设中断

### • 数字延时滤波

- 3 组独立配置延时滤波单元, 分别对应外部中断、功率保护和 CAP1/2/3

- 串行通讯外设

- -SCI

### 时钟

- -10M 片内振荡器

- -PLL 倍频系数 1x~15x

- ・支持 WDT

- 支持 4 线制快速程序烧录

- ・支持 JTAG 在线仿真

- 分析和断点功能

- 基于硬件的实时调试

- ESD 等级(HBM): 2000V

- ・ 温度范围: -40°C~125°C (通过 AEC-Q100)

- 结温: -40°C~150°C

- ・封装形式

- LQFP48 封装

- QFN48 封装

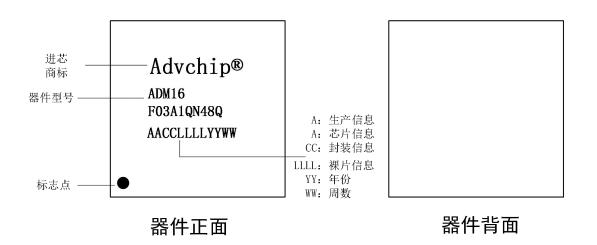

# 2. 型号命名规则

ADM16F03A1QN48Q产品命名规则:

### 器件标识:

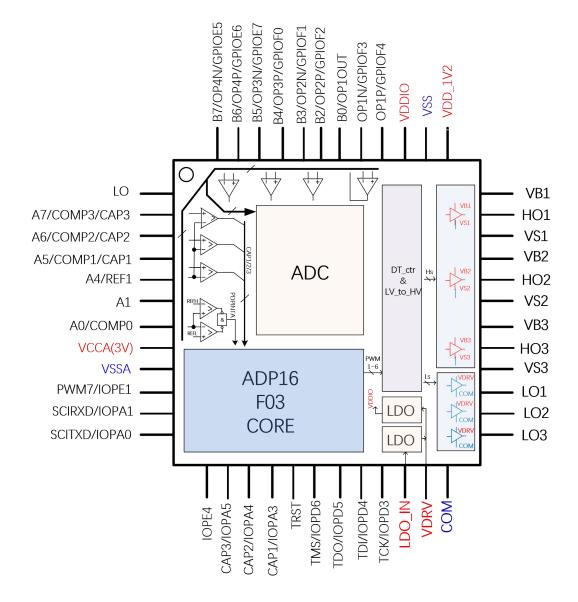

### 3. 系统概述

ADM16F03A1 是一款面向无刷电机控制应用场景开发的 16 位增强型 DSP 器件, 片上集成双 LDO, 支持单电源供电模式。改进型 DSP 处理器内核与运算加速单元, 同时主频可运行到 150MHz, 可满足多种类型电机应用算法的算力要求, 并配置事件管理器、SCI 模块、12 位 ADC、运算放大器、电压比较器、6NMOS 预驱模块, 有利于用户布板的极简化。

图 3.1 ADM16F03A1 系统框图

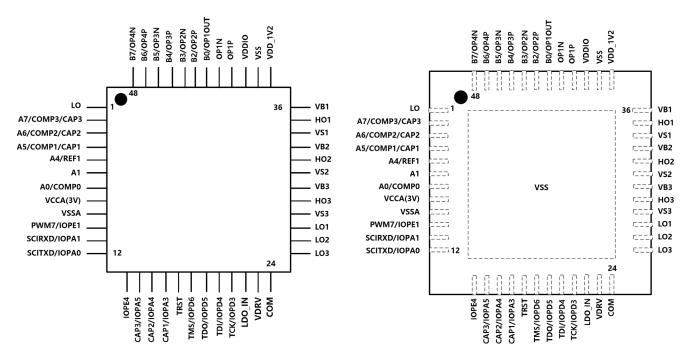

# 4. 引脚排布与说明

- A. GPIO 通用输入/输出引脚,所有 GPIO 在复位后默认为输入状态;

- B. 建议模拟电源地与数字电源地隔离以保持指定精度;

- C. PU 表示片内默认上拉, PD 表示片内默认下拉。

### 图 4. 1 ADM16F03A1 LQFP48 (左) 与 VQFN48 (右) 封装引脚排布

表 4. 1ADM16F03A1 芯片引脚功能定义

| 管脚 | 名称           | 类型          | PU/PD/Z | 功能说明                        |

|----|--------------|-------------|---------|-----------------------------|

| 1  | LO           | 电源          | -       | ADC 及运放参考地,连接至模拟地           |

| 2  | A7/ COMP3    | 模拟输入        | -       | ADC 输入 A7 或比较器 3 输入端        |

| 3  | A6/COMP2     | 模拟输入        | -       | ADC 输入 A6 或比较器 2 输入端        |

| 4  | A5/COMP1     | 模拟输入        | -       | ADC 输入 A5 或比较器 1 输入端        |

| 5  | A4/ REF1     | 模拟输入        | -       | ADC 输入 A4 或比较器 1、2、3 参考电压输入 |

| 6  | A1           | 模拟输入        | -       | ADC 输入 A1                   |

| 7  | A0/COMP0     | 模拟输入        | -       | ADC 输入 A0 或比较器 0 (双门限) 输入端  |

| 8  | VCCA         | 电源          | -       | 模拟 3.0V 电源,内部 LDO 产生        |

| 9  | VSSA         | 电源          | -       | 模拟地                         |

| 10 | PWM7/IOPE1   | 数字输入/输出     | PU      | PWM7 输出或 GPIOE1             |

| 11 | SCIRXD/IOPA1 | ¥たごな〉 /t◇ 川 | DII     | SCI 接收或 GPIOA1              |

| 12 | SCITXD/IOPA0 | 数字输入/输出     | PU      | SCI 发送或 GPIOA0              |

| 13 | IOPE4        | 数字输入/输出     | PU      | GPIOE4 或 Boot 引导分支控制        |

| 管脚 | 名称             | 类型        | PU/PD/Z | 功能说明                                     |

|----|----------------|-----------|---------|------------------------------------------|

| 14 | CAP3/IOPA5     |           |         | CAP3 或 GPIOA5                            |

| 15 | CAP2/IOPA4     | 数字输入/输出   | PU      | CAP2 或 GPIOA4                            |

| 16 | CAP1/IOPA3     |           |         | CAP1 或 GPIOA3                            |

| 17 | TRST           |           | PD      | JTAG 复位                                  |

| 18 | TMS/IOPD6      |           | PU      | JTAG 模式选择或 GPIOD6                        |

| 19 | TDO/IOPD5      | JTAG      | PD      | JTAG 串行输出或 GPIOD5                        |

| 20 | TDI/IOPD4      |           | PU      | JTAG 串行输入或 GPIOD4                        |

| 21 | TCK/IOPD3      |           | PU      | JTAG 时钟输入或 GPIOD3                        |

| 22 | LDO_IN         | 电源        | -       | LDO (母线) 输入引脚, 4.5~40V                   |

| 23 | VDRV           | 电源        | -       | 12V 预驱模拟电源,由内部 LDO 产生,外接 10ul<br>或更大滤波电容 |

| 24 | COM            | 电源        | _       | 预驱模拟电源参考地,外部需单点连接至 VSS                   |

| 25 | LO3            | 输出        | _       | 3-相低端驱动输出                                |

| 26 | LO2            | 输出        | _       | 2-相低端驱动输出                                |

| 27 | LO1            | 输出        | -       | 1-相低端驱动输出                                |

| 28 | VS3            | 电源        | -       | 3-相高端悬浮地                                 |

| 29 | ноз            | 输出        | -       | 3-相高端驱动输出                                |

| 30 | VB3            | 电源        | -       | 3-相自举高端电源                                |

| 31 | VS2            | 电源        | -       | 2-相高端悬浮地                                 |

| 32 | HO2            | 输出        | -       | 2-相高端驱动输出                                |

| 33 | VB2            | 电源        | -       | 2-相自举高端电源                                |

| 34 | VS1            | 电源        | -       | 1-相高端悬浮地                                 |

| 35 | HO1            | 输出        | -       | 1-相高端驱动输出                                |

| 36 | VB1            | 电源        | -       | 1-相自举高端电源                                |

| 37 | VDD_1V2        | 电源        | -       | 1.2V 内核电源输出,外接 2.2uF 电容                  |

| 38 | VSS            | 电源        | -       | 数字地                                      |

| 39 | VDDIO          | 电源        | -       | 3.3~5V 数字电源,外接 10uF+0.1uF 电容             |

| 40 | OP1P/GPIOF4    | 模拟输入      | -       | 运放 1 输入正端或 GPIOF4 输入                     |

| 41 | OP1N/GPIOF3    | 模拟输入      | -       | 运放 1 输入负端或 GPIOF3 输入                     |

| 42 | B0/OP1OUT      | 模拟输入/输出   | -       | ADC 输入 B0 或运放 1 输出端                      |

| 43 | B2/OP2P/GPIOF2 | 模拟输入/数字输入 | -       | ADC 输入 B2 或运放 2 输入正端或 GPIOF2 输入          |

| 44 | B3/OP2N/GPIOF1 | 模拟输入数字输入  | -       | ADC 输入 B3 运放 2 输入负端或 GPIOF1 输入           |

| 45 | B4/OP3P/GPIOF0 | 模拟输入数字输入  | -       | ADC 输入 B4 或运放 3 输入正端或 GPIOF0 输入          |

| 46 | B5/OP3N/GPIOE7 | 模拟输入数字输入  | -       | ADC 输入 B5 或运放 3 输入负端或 GPIOE7 输入          |

| 47 | B6/OP4P/GPIOE6 | 模拟输入数字输入  | -       | ADC 输入 B6 或运放 4 输入正端或 GPIOE6 输入          |

| 48 | B7/OP4N/GPIOE5 | 模拟输入数字输入  | -       | ADC 输入 B7 或运放 4 输入负端或 GPIOE5 输入          |

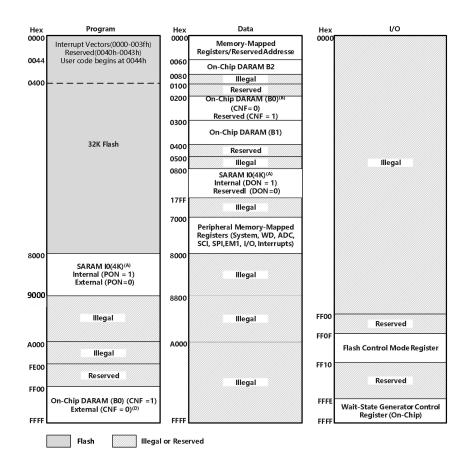

# 5. 内存映射

### 5.1 存储空间映射

- A. 单周期访问 RAM IO, 配置 PON, DON 选择映射到程序空间或数据空间;

- B. 双口 RAM BO, 通过配置 CNF 选择映射到程序空间或数据空间。

图 5.1 ADM16F03A1 存储空间映射

### 5.2 外设空间映射

图 5.2 ADM16F03A1 外设空间映射

# 6. 内核说明

### 6.1 内核结构原理

CPU 包括一个 16 位定标移位器,一个 16 位乘 16 位并行乘法器,一个 32 位中央算 术逻辑单元,一个 32 位累加器,以及用于累加器和乘法器输出的辅助移位器。CPU 的 功能模块如图 6-1 所示,表 6-1 列出了 CPU 内部硬件模块的功能。

图 6.1 CPU 功能模块框图

# 进版电子 Advancechip ADM16F03A1 Digital Signal Processor

### 表 6.1 CPU 内部硬件模块说明

| 模块符号        | 模块名称                                          | 模块功能描述                                                                                                                                           |  |

|-------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ACC         | 累加器                                           | 32 位寄存器,用于保存中央算术逻辑单元 CALU 的计算结果,并为下一次 CALU 运算<br>提供输入,具有移位和循环操作功能。                                                                               |  |

| ARAU        | 辅助寄存器算术单元                                     | 无符号的 16 位运算单元,当使用辅助寄存器作为输入输出,用于计算间接地址。                                                                                                           |  |

| AUX<br>REGS |                                               | 16 位寄存器用作指向任意数据空间地址的指针。这些寄存器通过 ARAU 操作,并由辅助寄存器指针(ARP)选定。ARO 可用作 ARx(x 为 1~7)超过 1 个发生更新时的索引值,也可作为 ARx 的比较值。                                       |  |

| С           | 进位标志位                                         | CALU 进位输出寄存器。此进位被反馈到 CALU 进行扩展算术运算。C 进位标志位分配于状态寄存器 1(ST1),可通过条件指令测试。也可以用于累加器移位和循环。                                                               |  |

| CALU        | 中央算术逻辑单元                                      | 32 位主算术逻辑单元,CALU 在单个机器周期中执行 32 位操作。CALU 对来自 ISCALE<br>或 PSCALE 的数据与来自 ACC 的数据进行运算操作,并将运算后结果保存到 PCTRL<br>单元。                                      |  |

| DARAM       |                                               | 当片上 RAM 配置控制位(CNF)被设置为 0,B0(DARAM)被映射到数据空间;反之,B0 被映射到程序空间。块 B1 和 B2 被映射到数据存储器空间,地址范围为0300h~03FFh 和 0060h~007Fh。B0 和 B1 容量均为 256 个字,B2 容量为 32 个字。 |  |

| DP          | 数据存储器页指针                                      | 9 位 DP 寄存器与指令字的 7 个最低有效位(LSBs)组合形成 16 位直接存储器地址。<br>DP 可以由 LST 和 LDP 指令修改。                                                                        |  |

| GREG        |                                               | GREG 设定全局数据存储空间的大小。由于在 ADM16F03A1 器件中没有使用全局内存空间,所以此寄存器功能保留。                                                                                      |  |

| IMR         | 中断屏蔽寄存器                                       | CPU 级中断使能屏蔽寄存器。IMR 寄存器可独立配置,用于屏蔽或使能对应的中断。                                                                                                        |  |

| IFR         | 中断标志寄存器                                       | CPU 级中断标志寄存器。                                                                                                                                    |  |

| INT#        | 中断陷阱                                          | 总共 32 个可通过硬件或软件方式产生的中断。                                                                                                                          |  |

| ISCALE      | 输入数据定标移位器                                     | 16 到 32 位的桶形左移位器。ISCALE 将输入的 16 位数据的 0 到 16 位在捕获周期内向<br>左移位,以得到 32 位输出,因此输入定标移位操作不需要额外周期。                                                        |  |

| MPY         | 乘法器                                           | 16x16 位乘法器,输出 32 位乘积。MPY 在单周期内执行乘法。MPY 可进行有符号或者无符号的二进制补码算术乘法。                                                                                    |  |

| MSTACK      | 微堆栈                                           | 当程序地址生成逻辑用作生成数据空间的连续地址时,MSTACK 用于临时存储下一条<br>待取址指令的地址。                                                                                            |  |

| MUX         | 多路选择器                                         | 将多路总线复用到一个公共输入。                                                                                                                                  |  |

| NPAR        | 下一个程序地址寄存<br>AR 器 NPAR 保存程序地址总线上下一个指令周期的程序地址。 |                                                                                                                                                  |  |

| OSCALE      | 输出数据定标寄存器                                     | 16 位到 32 位的桶形左移寄存器。OSCALE 将 32 位的累加器输出左移 0 到 7 位,用以实现数据归一化,并将移位后 32 位数据的高 16 位或者低 16 位输出到数据写总线(DWEB)。                                            |  |

| PAR         | 程序地址寄存器                                       | PAR 在完成与当前总线周期相关的所有内存操作前期间内,保存当前在 PAB 上运行地址。                                                                                                     |  |

| 模块符号   | 模块名称    | 模块功能描述                                                                                  |

|--------|---------|-----------------------------------------------------------------------------------------|

| PC     | 程序计数器   | PC 计数器每次将 NPAR 的值增加 1,为取指操作和连续数据传送操作输出连续地址。                                             |

| PCTRL  | 程序控制器   | PCTRL 解码指令,管理流水线,存储状态位,并对条件操作进行解码。                                                      |

| PREG   | 乘积寄存器   | 32 位寄存器,用于保存 16x16 的乘积。                                                                 |

| PSCALE | 乘积定标移位器 | 将乘法器乘积左移 0/1/4 位,或右移 6 位。左移可得到由二进制补码乘法运算产生的附加标志位。右移可用来将数字量按比例减少,以防止 CALU 内的乘积累加溢出。      |

| STACK  | 堆栈      | 堆栈是用于存储子程序和中断服务子程序返回地址的内存块,或者用于存储数据。<br>ADM16x 定义堆栈为 16 位位宽,8 级深度。                      |

| TREG   | 临时寄存器   | 16 位寄存器,用于保存乘法运算中的一个操作数。TREG 可以保存 LACT、ADDT 和<br>SUBT 指令的移位个数,TREG 也可保存 BITT 指令的测试位的位置。 |

### 6.2 系统寄存器

### 6.2.1 系统状态寄存器

CPU 集成两个系统状态寄存器,分别为 STO 和 ST1,包含多种条件和模式下的状态定义。这两个寄存器存储在数据地址,可从数据地址加载,并支持保存微处理器状态以及恢复子程序。

可通过状态寄存器加载指令(LST)对 STO 和 ST1 进行写入操作。存储状态寄存器指令(SST)用于从 STO 和 ST1 读取,(不受 LST 指令影响的 INTM 位除外)。可借助 SETC 和 CLRC 指令对其进行逐位写 1 或清 0。下文介绍了状态寄存器 STO 和 ST1 的构成,对每个状态寄存器中包含的所有状态位进行描述。状态寄存器包含部分保留位,对保留位的读操作返回值 1。下表列出了状态寄存器字段定义。

### 1.ST0 状态寄存器

| 15~13 | 12   | 11   | 10 | 9    | 8~0  |

|-------|------|------|----|------|------|

| ARP   | OV   | OVM  | 1  | INTM | DP   |

| RW_X  | RW_X | RW_X |    | RW_1 | RW_X |

注: R=可读, W=可写, C=清除, \_0=复位值;

ARP: 辅助寄存器指针。ARP选择用于直接寻址的 AR。ARP加载时,ARP中的旧值复制到 ARB 寄存器位 15~13中。使用直接寻址时,ARP可以通过存储相关指令例如 LARP,MAR,LST 指令修改。当 LST #1 指令执

| Advance |                                                                                                                                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 行时,ARP 加载与 ARB 相同的值。                                                                                                                                                                                    |

| 位 12    | OV: 溢出标志位。当算术逻辑单元产生溢出,溢出信号被锁存,OV 被置 1。溢出产生后,OV 将保持置位,直到 CPU 复位、对 OV/NOV 进行 BCND/D 操作,以及 LST 指令清除 OV 状态位。                                                                                                |

| 位 11    | OVM:溢出模式位。当 OVM 设置为 0,溢出结果在累加器上正常溢出,当设置为 1,溢出发生时累加器设置为最大正值或最小负值。SETC 指令和 CLRC 指令可对此位进行置位和清零操作。LST 指令也可以用来修改 OVM。                                                                                        |

| 位 9     | INTM:中断模式位。当 INTM 被设置为 0 代表所有的非屏蔽中断均启用。设置为 1 代表所有的屏蔽中断均为禁用状态。INTM 由 SETC INTM 和 CLRC INTM 指令置位与复位。RS 亦可设置 INTM。INTM 对不可屏蔽的 RS 和 NMI 中断没有影响。注意,INTM 不受 LST 指令的影响。系统复位时此位被默认置 1。当一个可屏蔽的中断陷阱被捕获时,它也被设置为 1。 |

| 位8~位0   | DP:数据存储器页指针。9位 DP 寄存器与指令字的7个最低有效位组合成16个位的直接存储器地址。DP可以通过LST和LDP指令修改。                                                                                                                                     |

### 2.ST1 状态寄存器

| <br>15~13 | 12  | 11 | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1~0 |

|-----------|-----|----|-----|---|---|---|---|---|---|---|---|-----|

| ARB       | CNF | TC | SXM | С | 1 | 1 | 1 | 1 | 1 | 1 | 1 | PM  |

RW\_X RW\_0 RW\_X RW\_1

RW\_00

注: R=可读, W=可写, C=清除, \_0=复位值;

| T .                                           |                                                          |

|-----------------------------------------------|----------------------------------------------------------|

| <br>  位 15~位 13                               | ARB:辅助寄存器指针缓存。当 ARP 被加载到 STO 时,旧的 ARP 值被复制到 ARB,除非       |

| <u>                                      </u> | 在一个 LST 指令中。当 ARB 通过一个 LST #1 指令加载时,同样的值也将复制到 ARP 中。     |

|                                               | CNF: 片内的 RAM 配置控制位。如果将 CNF 设置为 0,则可重新配置双寻址 RAM 块映        |

| 位 12                                          | 射到数据空间;反之,则映射到程序空间。CNF 可以通过 SETC CNF、CLRC CNF 和 LST      |

|                                               | #1 指令进行修改。系统复位时 CNF 为 0。                                 |

|                                               | TC:测试/控制标志位。TC 受 BIT, BITT, CMPR, LST # 1 和 NORM 指令的影响。当 |

| / <del>≥.</del> 11                            | BIT 或 BITT 中一个测试位为 1,或者 AR(ARP)和 ARO 之间存在 CMPR 比较测试条件,或  |

| <u>位</u> 11                                   | 者当测试 NORM 指令执行 OR 函数时累加器的 2 个最高有效位为 1 时 TC 被置位为 1。       |

|                                               | 条件跳转,调用和返回指令可基于 TC 条件执行。                                 |

|                                               | SXM: 符号扩展模式位。SXM=1 在数据通过定标移位器传递到累加器时产生符号扩展。              |

| / <del>∴</del> 10                             | SXM=0禁止符号扩展。SXM不影响某些指令的定义;例如 ADDS 指令,不管 SXM 如何,          |

| 位 10                                          | 都会禁止符号扩展。SXM 通过 SETC SXM 指令置 1,通过 CLRC SXM 指令复位清 0,且     |

|                                               | 可以通过 LST #1 指令加载。复位时 SXM 默认设置为 1。                        |

|                                               | C: 进位。如果加法运算结果产生一个进位,则 C 被置为 1,如果减法运算结果产生一个              |

|                                               | 借位,则 C 被复位为 0,反之,在加法后复位为 0 或减法之后被置位为 1,ADD 或带有           |

| 位 9                                           | 16 位移位的 SUB 指令除外。通常情况下,ADD 只能置位进位,SUB 只能复位进位,但           |

|                                               | 不能影响进位,单 bit 位的移位操作循环移位指令以及 SETC,CLRC 和 LST #1 指令均会影     |

|                                               | 响 C 的状态,复位时 C 被置位为 1。                                    |

|                                               | PM: 乘积移位方式                                               |

|                                               | PM=00,乘法器的 32 位乘积结果直接载入 CALU,不移位                         |

| 位 1~位 0                                       | PM=01,PREG 输出左移 1 位,最低位(LSB)以 0 填充后载入 CALU               |

|                                               | PM=10,PREG 输出左移 4 位,最低位(LSB)以 0 填充后载入 CALU               |

|                                               | PM=11,PREG 输出右移 6 位,并进行符号扩展                              |

注意: PREG 中的内容一直保持不变。当把 PREG 中的内容传送到 ALU 单元时,移位操作发生,PM 可由 SPM 指令和 LST #1 指令加载,复位时 PM 清 0。

### 6.2.2 系统控制寄存器

### 1. 系统控制寄存器 SCSR1—7018h

| 15              | 14         | 13         | 12        | 11        | 10         | 9       | 8       |

|-----------------|------------|------------|-----------|-----------|------------|---------|---------|

| W:pll_bypass_   | - 1        |            |           |           |            |         |         |

| R: pll_lock_flg | 保留位        | 保留位        | 保留位       | CLK_NS3   | CLK_NS2    | CLK_NS1 | CLK_NS0 |

| R_0             | RW_0       | RW_0       | RW_0      | RW_1      | RW_1       | RW_1    | RW_0    |

|                 |            |            |           |           |            |         |         |

| 7               | 6          | 5          | 4         | 3         | 2          | 1       | 0       |

| ADCCLK EN       | SCICLK EN  | SPICLK EN  | Auxiliary | Auxiliary | EM1CLK I   | EN 保留位  | ILLADR  |

| ADCCLK_LIN      | SCICER_LIN | SPICER_LIN | CLKEN 0   | CLKEN 1   | LIVITCER_I |         | ILLADK  |

| RW_0            | RW_0       | RW_0       | RW_0      | RW_0      | RW_0       | R_0     | RC_0    |

注: R=可读, W=可写, C=清除, \_0=复位值;

| 1       |                                                      |  |  |  |  |

|---------|------------------------------------------------------|--|--|--|--|

|         | PLL 时钟控制增加了 PLL 时钟在倍频锁定之前的 bypass 的功能,以保证内核稳定        |  |  |  |  |

|         | 工作,其中 SCSR1[15]在读、写时具有不同的含义,写入时是开启 PLL 倍频锁定          |  |  |  |  |

| 位 15    | 之前 bypass 控制的使能位,写入 1 代表 bypass 控制使能,默认开启,写入 0 则     |  |  |  |  |

| 12 13   | 不开启 PLL 倍频锁定之前 bypass 的功能,即 PLL 输出直接送入内核。读 SCSR1[15] |  |  |  |  |

|         | 的含义是判断 PLL 是否锁定,若读出来的 SCSR1[15]是逻辑 1,则表示 PLL 已锁      |  |  |  |  |

|         | 定,反之则表示 PLL 还未锁定。                                    |  |  |  |  |

| 位 14    | 保留                                                   |  |  |  |  |

| 位 13~12 | 保留                                                   |  |  |  |  |

| 0.44    | CLK_NS3~ CLK_NS0: PLL 倍频系数选择;                        |  |  |  |  |

| 位 11~8  | 详见表 8-1 通过 SCSR1 (0x7018) 寄存器选择 PLL 时钟               |  |  |  |  |

|         | ADCCLK_EN:ADC 模块时钟使能控制位;                             |  |  |  |  |

| 位 7     | 0:禁用 ADC 模块时钟(即:关断 ADC 模块,以降低功耗);                    |  |  |  |  |

|         | 1:使能 ADC 模块时钟;                                       |  |  |  |  |

|         | SCICLK_EN: SCI 模块时钟使能控制位;                            |  |  |  |  |

| 位 6     | 0:禁用 SCI 模块时钟 (即:关断 SCI 模块,以降低功耗);                   |  |  |  |  |

|         | 1: 使能 SCI 模块时钟;                                      |  |  |  |  |

|         | SPICLK_EN: SPI 模块时钟使能控制位;                            |  |  |  |  |

| 位 5     | 0:禁用 SPI 模块时钟 (即:关断 SPI 模块,以降低功耗);                   |  |  |  |  |

|     | 1:使能 SPI 模块时钟;                                   |  |  |  |  |  |  |

|-----|--------------------------------------------------|--|--|--|--|--|--|

|     | Auxiliary CLKEN 0:辅助寄存器 0 时钟使能控制位,辅助寄存器 0 包括运放和电 |  |  |  |  |  |  |

| 位 4 | 压比较器模块的寄存器;                                      |  |  |  |  |  |  |

|     | 0: 禁用辅助寄存器 0 时钟;                                 |  |  |  |  |  |  |

|     | 1: 使能辅助寄存器 0 时钟;                                 |  |  |  |  |  |  |

|     | Auxiliary CLKEN 1:辅助寄存器 1 时钟使能控制位,辅助寄存器 1 包括     |  |  |  |  |  |  |

|     | T7,T8,PWM7/PWM8,Cache 和数字延时滤波模块的寄存器,加速运算单元的寄     |  |  |  |  |  |  |

| 位 3 | 存器;                                              |  |  |  |  |  |  |

|     | 0: 禁用辅助寄存器 1 时钟;                                 |  |  |  |  |  |  |

|     | 1: 使能辅助寄存器 1 时钟;                                 |  |  |  |  |  |  |

|     | EM1CLK_EN:EM1 模块时钟使能控制位;                         |  |  |  |  |  |  |

| 位 2 | 0:禁用 EM1 模块时钟 (即:关断 EM1 模块,以降低功耗);               |  |  |  |  |  |  |

|     | 1: 使能 EM1 模块时钟;                                  |  |  |  |  |  |  |

| 位 1 | 保留                                               |  |  |  |  |  |  |

| 位 0 | ILLDR: 无效地址检测位;                                  |  |  |  |  |  |  |

### 2. 系统控制寄存器 SCSR2—7019h

| 15   | 14   | 13             | 12   | 11   | 10   | 9    | 8    |  |  |  |

|------|------|----------------|------|------|------|------|------|--|--|--|

|      | 保留位  |                |      |      |      |      |      |  |  |  |

|      | RW_0 |                |      |      |      |      |      |  |  |  |

| 7    | 6    | 5              | 4    | 3    | 2    | 1    | 0    |  |  |  |

| 保留位  | 保留位  | WD<br>OVERRIDE | 保留位  | 保留位  | 保留位  | DON  | PON  |  |  |  |

| RW_0 | RW_0 | RC_1           | RW_0 | RW_1 | RW_0 | RW_1 | RW_1 |  |  |  |

注: R=可读, W=可写, C=清除, \_0=复位值, S=只可被置位;

| 位 15~位 7 | 保留                                                                                                                                                                          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 位 6      | 保留                                                                                                                                                                          |

| 位 5      | WD OVERRIDE: WD 保护位,复位时默认值为 1,允许用户通过软件将 WDCR 寄存器中的 WDDIS 位置 1 禁止 WD 工作,该位是一个只能清 0 位,通过向该位写 1 对其清 0; 0:使用户不能通过软件来禁止 WD。该位是一个只能清 0 位,不能通过软件来置 1; 1:复位时默认值,使用户能够通过软件来禁止 WD 工作; |

| 位 4      | 保留                                                                                                                                                                          |

| 位 3      | 保留                                                                                                                                                                          |

#

V1.4

|           |       |      | <u> </u>                 |

|-----------|-------|------|--------------------------|

| 位 2       | 保留    |      |                          |

|           | SARAI | M 程序 | /数据空间选择位。                |

|           | DON   | PON  | I SARAM 状态;              |

|           | 0     | 0    | 地址空间不被映射;                |

| 位 1 ~ 位 0 | 0     | 1    | SARAM 被映射到片上程序空间;        |

|           | 1     | 0    | SARAM 被映射到片上数据空间;        |

|           | 1     | 1    | SARAM 被同时映射到片上程序空间和数据空间; |

### 7 存储系统

### 7.1 片上存储器

该系列器件配置如下内存模块:

- 4K x 16 位 SARAM

- (256+256+32) 544x 16 位 DARAM

- 32K x 16 位 Flash

### 7.2 双存取 RAM (DARAM)

该系列器件上包含 544 字×16 位的 DARAM。DARAM 允许在同一个周期内对 RAM 进行写入和读取。DARAM 配置为三个块:块0 (B0),块1 (B1)和块2 (B2)。块1 包含 256 个字,块2 包含 32 个字,并且这两个块仅映隐射到数据存储空间。块0 包含 256 个字,可以配置为数据空间或程序空间。SETC CNF (将 B0 配置为程序存储器)和 CLRC CNF (将 B0 配置为数据存储器)指令可用作允许通过软件动态配置存储器映射。

代码在 RAM 中运行时可达到 CPU 主频速率,无需配置等待状态。DARAM 允许在一个周期内执行两次访问。

# 7.3 单存取 RAM (SARAM)

该系列器件包含一块 4Kx16 位 IO SARAM,通过 SCSR2 寄存器 PON 和 DON 位配置为数据存储器、或程序存储器或程序空间与数据空间共用,有关 SCSR2 寄存器的 PON 和 DON 位配置详细信息,可请参考见 SCSR2 寄存器描述表。复位时,PON 和 DON 为 11,片上 SARAM 同时映射到程序空间和数据空间。

### 7.4 闪存 Flash

### 7.4.1 Flash 说明

### ADM16F03A1 Digital Signal Processor

该系列器件集成一块片上闪存,大小为 32K\*16bit,映射的程序地址段为 0000h~7FFFh。其中,中断向量表空间 0000h~003Fh,保留地址段 0040~0043h 为代码安全密码。

闪存空间被分为四个扇区,扇区 0 大小为 4K\*16bit,映射到地址段 0000h~0FFFh,扇区 1 大小为 12K\*16bit,映射到地址段 1000h~3FFFh,扇区 2 大小为 12K\*16bit,映射地址段 4000h~6FFFh,扇区 3 大小为 4K\*16bit,映射到地址段 7000h~7FFFh。

### 7.4.2 唯一 ID

该系列器件设有唯一ID编码。器件完成上电完成后唯一ID编码被加载到寄存器 0X752D, 0X752C, 0X752B, 0X752A。这些寄存器均为只读寄存器。

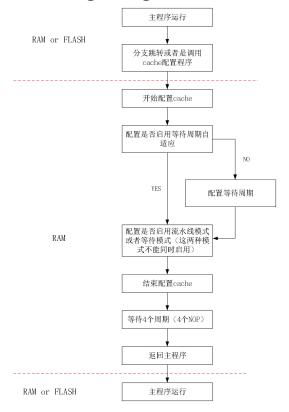

### 7.4.3 Cache 说明

### 1. Cache 功能描述

- 1) 工作模式可配置为流水线模式或等待模式

- 2) 等待时钟周期支持用户配置或根据系统时钟频率自动调节

- 3) 缓存容量: 64bit

- 4) Cache 功能可软件关闭

- 5) 等待模式时,每当高位地址(最高位到 bit2 位)变化时,等待相应的时钟周期数(WaitNum);流水线模式时,每当高位地址(最高位到 bit2 位)变化不连续时(地址不连续),等待相应时钟周期数(WaitNum)。

### 2.配置流程

#### 备注:

- A. 禁止在 Flash 中运行 Cache 的配置代码;

- B. 配置过程应遵循上述图示流程;

- C. 系统时钟周期高于 45ns, 无需启用 Cache;

- D. 等待周期计算方法:

WaitNum= (45ns) /系统时钟周期; 去尾法取整;

E. 要使用 Cache 必须开启 PLL 倍频锁定之前 bypass 功能。

图 7.1 Cache 配置流程图

### 3. Cache 控制寄存器—753Eh

| 15      | 14      | 13               | 12   | 11    | 10   | 9       | 8          |

|---------|---------|------------------|------|-------|------|---------|------------|

| PWM8_EN | PWM7_EN | PWM8_OUT<br>_PAD | 保留位  | 保留位   | 保留位  | PipeEn  | WaitModeEn |

| RW_0    | RW_0    | RW_0             | RW_0 | RW_0  | RW_0 | RW_0    | RW_0       |

| 7       | 6       | 5                | 4    | 3     | 2    | 1       | 0          |

| 保留位     | 保留位     | 保留位              | 保留位  | AutoF |      | WaitNur | n          |

| RW_0    | R_1     | R_1              | RW_0 | RW_0  | RW_0 | RW_0    | RW_0       |

注: R=可读, W=可写, C=清除, \_0=复位值, \_1=复位值;

|           | PWM8_EN: PWM8 使能位;                    |

|-----------|---------------------------------------|

| 位 15      | 0: 禁止 PWM8 输出;                        |

|           | 1: 使能 PWM8 输出;                        |

|           | PWM7_EN: PWM7 使能位;                    |

| 位 14      | 0: 禁止 PWM7 输出;                        |

|           | 1: 使能 PWM7 输出;                        |

|           | PWM8_OUT_PAD: 使能 PWM8 输出到 pad;        |

| 位 13      | 0: 禁止 PWM8 输出到 pad;                   |

|           | 1:使能 PWM8 输出到 pad ;                   |

| 位 12~位 10 | 保留                                    |

|           | PipeEn: 流水线模式使能位:                     |

| 位 9       | 1: 启用流水线模式;                           |

|           | 0: 关闭流水线模式;                           |

|           | WaitModeEn:等待模式使能位:                   |

| 位 8       | 1: 启用等待模式;                            |

|           | 0: 关闭等待模式;                            |

| 位 7~位4    | 保留                                    |

|           | AutoF: 频率自适应使能位:                      |

| 位 3       | 1: 等待周期根据频率自动调整;                      |

|           | 0:等待周期为 WaitNum 中的配置值;                |

|           | WaitNum:等待周期控制位,读取 flash 中的数据需要等待的周期。 |

| 42 42     | 当 AutoF=1 时,此位不用配置。                   |

| 位 2~位 0   | 当 AutoF=0 时:                          |

|           | WaitNum=(45ns/系统时钟周期);去尾法取整;          |

- 1) Cache 控制寄存器在使用前应先使能辅助寄存器 1 的时钟;

- 2) 流水线模式和等待模式同时启用时,等待模式优先级更高。

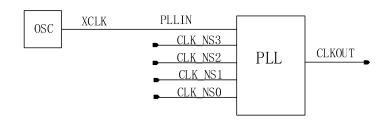

### 8 时钟系统

### 8.1 PLL 时钟模块

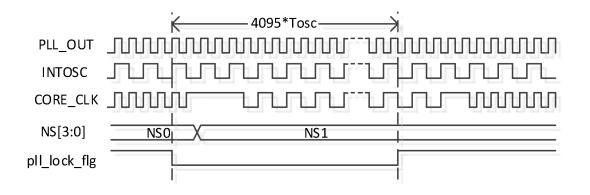

该系列器件集成一个片载、基于 PLL 的时钟模块。此模块为器件提供所有需要的时钟信号,以及控制器件进入低功耗模式。PLL 通过 4 个 bit 位 SCSR1[11:8],CLK\_NS3, CLK NS2, CLK NS1, CLK NS0 控制和选择不同的 CPU 时钟频率。

PLL 时钟控制增加了 PLL 时钟在倍频锁定之前的旁路功能,以保证内核稳定工作,其中 SCSR1[15]在读、写具有不同的含义,写操作代表开启 PLL 倍频锁定之前 bypass 控制的使能位,写入 1 开启,默认开启,写入 0 则不开启 PLL 倍频锁定之前 bypass 的功能,即 PLL 输出直接送入内核。读 SCSR1[15]的含义是判断 PLL 是否锁定,若读出来的 SCSR1[15]是逻辑 1,则表示 PLL 已锁定,反之则表示 PLL 还未锁定。

图 8.1 PLL 时钟模块功能框图

图 8.2 PLL 时钟旁路控制信号时序

# 进版电子 Advancechip ADM16F03A1 Digital Signal Processor

### 表 8. 1 SCSR1 寄存器配置 PLL 倍频系数表

| CLK NS[3:0] | PLLOUT    | CLK NS[3:0] | PLLOUT    |

|-------------|-----------|-------------|-----------|

| 0000        | PLLIN *1  | 0001        | PLLIN *1  |

| 0010        | PLLIN *2  | 0011        | PLLIN *3  |

| 0100        | PLLIN *4  | 0101        | PLLIN *5  |

| 0110        | PLLIN *6  | 0111        | PLLIN *7  |

| 1000        | PLLIN *8  | 1001        | PLLIN *9  |

| 1010        | PLLIN *10 | 1011        | PLLIN *11 |

| 1100        | PLLIN *12 | 1101        | PLLIN *13 |

| 1110        | PLLIN *14 | 1111        | PLLIN *15 |

# 8.2 PLL 时钟模块控制寄存器

### 1. 系统控制寄存器 SCSR1—7018h

| 15                                 |                                                                                                                                                                                                                                                     | 14     | 13                         | 12                   | 11                   | 10        | 9       | 8       |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------|----------------------|----------------------|-----------|---------|---------|

| W:pll_bypass_en<br>R: pll_lock_flg |                                                                                                                                                                                                                                                     | 保留位    | · 保留位                      | 保留位                  | CLK_NS3              | CLK_NS2   | CLK_NS1 | CLK_NS0 |

| R_0                                |                                                                                                                                                                                                                                                     | RW_0   | RW_0                       | RW_0                 | RW_1                 | RW_1      | RW_1    | RW_0    |

| 注: R=可读                            | , W=ī                                                                                                                                                                                                                                               | 可写,C=  | 清除,_0=复位·                  | 值;                   |                      |           |         |         |

| 7                                  |                                                                                                                                                                                                                                                     | 6      | 5                          | 4                    | 3                    | 2         | 1       | 0       |

| ADCCLK_EN                          | SCI                                                                                                                                                                                                                                                 | CLK_EN | SPICLK_EN                  | Auxiliary<br>CLKEN 0 | Auxiliary<br>CLKEN 1 | EM1CLK_EN | 保留位     | ILLADR  |

| RW_0                               | F                                                                                                                                                                                                                                                   | RW_0   | RW_0                       | RW_0                 | RW_0                 | RW_0      | R_0     | RC_0    |

| 位 15                               | PLL 时钟控制增加了 PLL 时钟在倍频锁定之前的 bypass 的功能,以保证内核稳定工作,其中 SCSR1[15]在读写时分别具有不同的含义,写入时是开启 PLL 倍频锁定之前 bypass 控制的使能 位,"1"有效,默认开启,若是"0"则不开启 PLL 倍频锁定之前 bypass 的功能,即 PLL 输出 直接送入内核。读 SCSR1[15]的含义是判断 PLL 是否锁定,若读出来的 SCSR1[15]是"1",则表示 PLL 已锁定,若是"0"则表示 PLL 还未锁定。 |        |                            |                      |                      |           |         |         |

| 位 14                               | 保留                                                                                                                                                                                                                                                  |        |                            |                      |                      |           |         |         |

| 位 13~12                            | 保留                                                                                                                                                                                                                                                  |        |                            |                      |                      |           |         |         |

| 位 11~8                             | _                                                                                                                                                                                                                                                   |        | 《_NS0: PLL 倍<br>8-1 通过 SCS |                      | )寄存器选择               | S PLL 时钟  |         |         |

| 位 7                                | 详细配置参考表 8-1 通过 SCSR1 (0x7018) 寄存器选择 PLL 时钟         ADCCLK_EN: ADC 模块时钟使能控制位;         0: 禁用 ADC 模块时钟 (关断 ADC 模块时钟可降低功耗);         1: 使能 ADC 模块时钟;                                                                                                     |        |                            |                      |                      |           |         |         |

| 位 6                                |                                                                                                                                                                                                                                                     | _      | CI 模块时钟使能块时钟 (关断           |                      | 中可降低功耗)              | ;         |         |         |

# 进版电子 Advancechip ADM16F03A1 Digital Signal Processor

|     | 1: 使能 SCI 模块时钟;                                                |

|-----|----------------------------------------------------------------|

|     | SPICLK_EN: SPI 模块时钟使能控制位;                                      |

| 位 5 | 0: 禁用 SPI 模块时钟 (关断 SPI 模块时钟可降低功耗);                             |

|     | 1:使能 SPI 模块时钟;                                                 |

|     | Auxiliary CLKEN 0: 辅助寄存器 0 时钟使能控制位, 辅助寄存器 0 包括运放相关寄存器与电压比      |

| 位 4 | 较相关寄存器;                                                        |

|     | 0: 禁用辅助寄存器 0 时钟;                                               |

|     | 1: 使能辅助寄存器 0 时钟;                                               |

|     | Auxiliary CLKEN 1: 辅助寄存器 1 时钟使能控制位。辅助寄存器 1 包含 T7、T8、PWM7、PWM8, |

|     | Cache 模块、数字延时滤波以及加速运算单元寄存器;                                    |

| 位3  | 0: 禁用辅助寄存器 1 时钟;                                               |

|     | 1: 使能辅助寄存器 1 时钟;                                               |

|     | EM1CLK_EN: EM1 模块时钟使能控制位;                                      |

| 位 2 | 0:禁用 EM1 模块时钟 (关断 EM1 模块时钟可降低功耗);                              |

|     | 1: 使能 EM1 模块时钟;                                                |

| 位1  | 保留                                                             |

| 位 0 | ILLDR: 无效地址检测位;                                                |

# 8.3 片内高精度 OSC

该系列器件集成高精度无引脚 OSC 模块,为 PLL 模块提供时钟源,无需片外晶振。 OSC 的典型输出频率为 10MHz, 其指标参数如表 8.2 所示:

表 8. 2 OSC 的指标参数

| 指标参数              | 最小值   | 典型值    | 最大值    | 单位  |

|-------------------|-------|--------|--------|-----|

| OSC 在-40℃~125℃时频率 | 9.800 | 10.000 | 10.200 | MHz |

### 9 中断系统

### 9.1 中断系统结构

该系列器件集成软件可编程中断,结构灵活且支持片上和外部中断配置,以满足高实时应用中的中断响应需求。可识别的中断源包括下述三种类型。

- 复位(由硬件或软件触发)不受 CPU 的限制,并立即优先于任意其它执行功能。所有可屏蔽的中断都被禁用,直到复位后用户程序启用。

- 器件复位源:一个看门狗定时器超时(复位)。

- 硬件产生的中断请求有外部引脚和片上外设请求。这两种类型如下:

- 外部中断请求由 XINT1、XINT2 和电压比较器(输入到 PDPINTA 信号)产生。

这三个外部中断信号由 CPU 的中断屏蔽寄存器 (IMR) 使能或者屏蔽,IMR 寄存器可以屏蔽 DSP 内核任一可屏蔽中断线。

- 外设中断是由片上事件管理器 EM1, SPI, SCI, ADC 外设模块事件触发产生。

它们可以通过每个外设中的特定事件的使能位以及 CPU 的 IMR 来屏蔽, IMR 寄存器可以屏蔽 DSP 内核任一可屏蔽中断线。

- 该系列器件的软件产生的中断包括:

- INTR 指令。该指令允许用软件初始化任一中断。其操作数表示 CPU 分支到的中断向量位置。该指令可禁止全局可屏蔽中断(将 INTM 位置 1)。

- NMI 指令。该指令迫使分支中断向量指向位置 24H。该指令可禁止全局可屏蔽中断。该系列器件未配置 NMI 硬件信号,仅支持软件触发。

- TRAP 指令。该指令迫使 CPU 分支到指向位置 22H 的中断向量。TRAP 指令不能禁止可屏蔽中断(INTM 未设置为 1)因此,当 CPU 分支到 TRAP 中断服务程序时,仍可触发响应其它可屏蔽硬件中断。

- 一 仿真器陷阱。该中断可以通过 INTR 指令或 TRAP 指令产生。

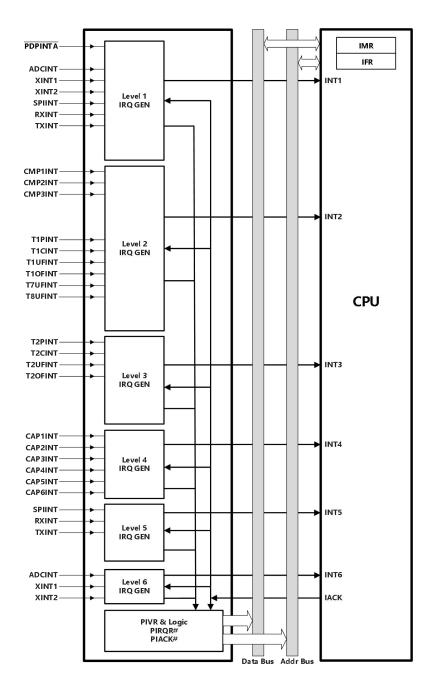

六个内核中断 (INT1-INT6) 前级通过外设中断扩展(PIE)进行控制, PIE 管理来自外设级中断,并分组到六个内核中断。PIE 中断硬件结构框架如图 9.1 所示,表 9.1 列举出PIE 与 CPU 中断向量对应关系。

图 9.1 PIE 中断硬件结构框架

#

### 表 9.1 中断源优先级与中断向量表

| 1        |     | 1              |                                 |                 |                 |            |                       |

|----------|-----|----------------|---------------------------------|-----------------|-----------------|------------|-----------------------|

| 中断名称     | 优先级 | CPU 中断向<br>量地址 | PIRQRx 和<br>PIACKRx<br>对应 bit 位 | 外设中断向<br>量(PIE) | 中断是<br>否可屏<br>蔽 | 外设模块       | 描述                    |

| Reset    | 1   | RSN<br>0000h   |                                 | N/A             | 否               | RS引脚,看门狗   | 管脚复位,看门狗超<br>时复位      |

| Reserved | 2   | -<br>0026h     |                                 | N/A             | 否               | СРИ        | <br>  仿真器陷阱<br>       |

| NMI      | 3   | NMI<br>0024h   |                                 | N/A             | 否               | 非屏蔽中断      | 不可屏蔽中断, 软件            |

| PDPINTA  | 4   | 902            | 0.0                             | 0020h           | 是               | EM1        | 电力设备保护中断引 脚           |

| ADCINT   | 5   |                | 0.1                             | 0004h           | 是               | ADC        | ADC 中断 (高优先级模式)       |

| XINT1    | 6   |                | 0.2                             | 0001h           | 是               | 外部中断逻辑     | 外部中断引脚                |

| XINT2    | 7   | INT1<br>0002h  | 0.3                             | 0011h           | 是               | 外部中断逻辑     | (高优先进模式)              |

| SPIINT   | 8   |                | 0.4                             | 0005h           | 是               | SPI        | SPI 中断引脚(高优<br>先级模式)  |

| RXINT    | 9   |                | 0.5                             | 0006h           | 是               | SCI        | SCI 接收中断(高优<br>先级模式)  |

| TXINT    | 10  |                | 0.6                             | 0007h           | 是               | SCI        | SCI 发送中断 (高优<br>先级模式) |

| CMP1INT  | 11  |                | 0.9                             | 0021h           | 是               | EM1        | 比较器 1 产生中断            |

| CMP2INT  | 12  |                | 0.10                            | 0022h           | 是               | EM1        | <br>  比较器 2 产生中断<br>  |

| CMP3INT  | 13  |                | 0.11                            | 0023h           | 是               | EM1        | 比较器 3 产生中断            |

| T1PINT   | 14  | INT2<br>0004h  | 0.12 0027h 是 EM1                |                 | EM1             | 定时器 1 周期中断 |                       |

| T1CINT   | 15  |                | 0.13                            | 0028h           | 是               | EM1        | 定时器 1 比较中断            |

| T1UFINT  | 16  |                | 0.14                            | 0029h           | 是               | EM1        | 定时器 1 下溢中断            |

| T10FINT  | 17  |                | 0.15                            | 002Ah           | 是               | EM1        | 定时器 1 溢出中断            |

| T7UFINT  | 18  |                | 2.6                             | 0031h           | 是               | EM1        | 定时器 7 下溢中断            |

ADM16F03A1 Digital Signal Processor

V1.4

|                |     | DIVITOR OF      |      | 21 <b>5</b> 1101 |     | 301    | , 1111               |

|----------------|-----|-----------------|------|------------------|-----|--------|----------------------|

| T8UFINT        | 19  |                 | 2.7  | 0032h            | 是   | EM1    | 定时器8下溢中断             |

| T2PINT         | 20  |                 | 1.0  | 002Bh            | 是   | EM1    | 定时器 2 周期中断           |

| T2CINT         | 21  | INT3            | 1.1  | 002Ch            | 是   | EM1    | 定时器 2 比较中断           |

| T2UFINT        | 22  | 0006h           | 1.2  | 002Dh            | 是   | EM1    | 定时器 2 下溢中断           |

| T2OFINT        | 23  |                 | 1.3  | 002Eh            | 是   | EM1    | 定时器 2 溢出中断           |

| CAP1INT        | 24  | INT4<br>- 0008h | 1.4  | 0033h            | 是   | EM1    | 捕获 1 中断              |

| CAP2INT        | 25  |                 | 1.5  | 0034h            | 是   | EM1    | 捕获 2 中断              |

| CAP3INT        | 26  |                 | 1.6  | 0035h            | 是   | EM1    | 捕获 3 中断              |

| SPIINT         | 27  |                 | 1.7  | 0005h            | 是   | SPI    | SPI 中断(低优先级)         |

| RXINT          | 28  | INT5<br>000Ah   | 1.8  | 0006h            | 是   | SCI    | SCI接收中断<br>(低优先级模式)  |

| TXINT          | 29  |                 | 1.9  | 0007h            | 是   | SCI    | SCI 发送中断<br>(低优先级模式) |

| ADCINT         | 30  |                 | 1.12 | 0004h            | 是   | ADC    | ADC 中断 (低优先级模式)      |

| XINT1          | 31  | INT6<br>000Ch   | 1.13 | 0001h            | 是   | 外部中断逻辑 | 外部中断引脚               |

| XINT2          | 32  |                 | 1.14 | 0011h            | 是   | 外部中断逻辑 | (低优先级模式)             |

| 保留的            |     | 000Eh           |      | N/A              | 是   | 中央处理器  | 保留                   |

| 陷阱             | N/A | 0022h           |      | N/A              | N/A | 中央处理器  | TRAP 指令              |

| 伪中断向<br>量      | N/A | N/A             |      | 0000h            | N/A | 中央处理器  | 伪中断向量                |

| INT8-<br>INT16 | N/A | 0010h-<br>0020h |      | N/A              | N/A | 中央处理器  | - 软件中断向量             |

| INT20-<br>IN31 | N/A | 0028h-<br>003Fh |      | N/A              | N/A | 中央处理器  | +A计中的112里<br>        |

# 9.2 CPU 中断寄存器

CPU 中断寄存器包括:中断标志寄存器 (IFR) 和中断屏蔽寄存器 (IMR)

### 1. CPU 中断标志寄存器 IFR—0006h

| 15~6 | 5         | 4         | 3         | 2         | 1         | 0         |

|------|-----------|-----------|-----------|-----------|-----------|-----------|

| 保留位  | INT6 flag | INT5 flag | INT4 flag | INT3 flag | INT2 flag | INT1 flag |

| 0    | RW 0      | RW 0      | RW 0      | RW 0      | RW 0      | RW 0      |

注: R=可读, W=可写, C=清除, 0=复位值, S=只可被置位;

| 位 15~6         | 保留位                                             |

|----------------|-------------------------------------------------|

| <u>M</u> 13.50 | INT6 flag:中断 6 标志位,该位用作连至第 6 级中断 INT6 的所有中断标志;  |

| 位 5            | 0 : 无 INT6 的中断挂起;                               |

| <u>1</u> Ω 3   | 1 : 至少一个 INT6 的中断挂起,对该位写 1 可清除此中断请求状态。          |

|                | INT5 flag:中断 5 标志位,该位用作连至第 5 级中断 INT5 的所有中断标志;  |

| 位 4            | 0 : 无 INT5 的中断挂起;                               |

|                | 1 : 至少一个 INT5 的中断挂起,对该位写 1 可清除此中断请求状态。          |

|                | INT4lag:中断 4 标志位,该位用作连至第 4 级中断 INT4 的所有中断标志;    |

| 位 3            | 0 : 无 INT4 的中断挂起;                               |

|                | 1 : 至少一个 INT4 的中断挂起,对该位写 1 可清除此中断请求状态。          |

|                | INT3 flag: 中断 3 标志位,该位用作连至第 3 级中断 INT3 的所有中断标志; |

| 位 2            | 0 : 无 INT3 的中断挂起;                               |

|                | 1 : 至少一个 INT3 的中断挂起,对该位写 1 可清除此中断请求状态。          |

|                | INT2 flag: 中断 2 标志位,该位用作连至第 2 级中断 INT2 的所有中断标志; |

| 位 1            | 0 : 无 INT2 的中断挂起;                               |

|                | 1 : 至少一个 INT2 的中断悬挂,对该位写 1 可清除此中断请求状态。          |

|                | INT1 flag: 中断 1 标志位,该位用作连至第 1 级中断 INT1 的所有中断标志; |

| 位 0            | 0 : 无 INT1 的中断挂起;                               |

|                | 1 : 至少一个 INT1 的中断挂起,对该位写 1 可清除此中断请求状态。          |

### 2. CPU 中断屏蔽寄存器 IMR—0004h

|   | 15~6                             | 5         | 4         | 3         | 2         | 1         | 0         |  |

|---|----------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|--|

|   | 保留位                              | INT6 mask | INT5 mask | INT4 mask | INT3 mask | INT2 mask | INT1 mask |  |

|   | _0                               | RW_0      | RW_0      | RW_0      | RW_0      | RW_0      | RW_0      |  |

| 洁 | 注:R=可读,W=可写,C=清除,_0=复位值,S=只可被置位; |           |           |           |           |           |           |  |

| 位 15~6 | 保留位                   |

|--------|-----------------------|

|        | INT6 mask: 中断 6 的屏蔽位; |

| 位 5    | 0 : 屏蔽中断 INT6;        |

|        | 1 : 使能中断 INT6;        |

| / 4    | INT5 mask: 中断 5 的屏蔽位; |

| 位 4    | 0 : 屏蔽中断 INT5;        |

|     | The first of the Digital Signal Frocessor | L • T |

|-----|-------------------------------------------|-------|

|     | 1 : 使能中断 INT5;                            |       |

|     | INT4 mask: 中断 4 的屏蔽位;                     |       |

| 位3  | 0 : 屏蔽中断 INT4;                            |       |

|     | 1 : 使能中断 INT4;                            |       |

|     | INT3 mask: 中断 3 的屏蔽位;                     |       |

| 位 2 | 0 : 屏蔽中断 INT3;                            |       |

|     | 1 : 使能中断 INT3;                            |       |

|     | INT2 mask: 中断 2 的屏蔽位;                     |       |

| 位 1 | 0 : 屏蔽中断 INT2;                            |       |

|     | 1 : 使能中断 INT2;                            |       |

|     | INT1 mask: 中断 1 的屏蔽位;                     |       |

| 位 0 | 0 : 屏蔽中断 INT1;                            |       |

|     | 1 : 使能中断 INT1;                            |       |

### 9.3 外设中断控制寄存器

外设中断寄存器包括:

外设中断向量寄存器;

外设中断请求寄存器 0/1/2 (PIRQR0/1/2);

外设中断应答寄存器 0/1/2 (PIACKR0/1/2);

外设中断请求寄存器 0/1/2 和外设中断应答寄存器 0/1/2 都属于外设中断扩展模块。 用来向 CPU 产生 INT1~INT6 中断请求的内部寄存器。这些寄存器用于调试使用,用户 可忽略。

### 1.外设中断向量寄存器 PIVR—701Eh

| 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| V15 | V14 | V13 | V12 | V11 | V10 | V9 | V8 | V7 | V6 | V5 | V4 | V3 | V2 | V1 | V0 |

$RW_0$

注: R=可读, W=可写, C=清除, 0=复位值, S=只可被置位;

| 位 15~0 | V15~V0:中断向量 V15~V0 位。该寄存器保存了最近一次应答外设中断的地址向量 |

|--------|---------------------------------------------|

### 2.外设中断请求寄存器 PIRQR0—7010h

| 15      | 14      | 13      | 12      | 11      | 10      | 9      | 8      |

|---------|---------|---------|---------|---------|---------|--------|--------|

| IRQ0.15 | IRQ0.14 | IRQ0.13 | IRQ0.12 | IRQ0.11 | IRQ0.10 | IRQ0.9 | 保留     |

| RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0   | RW_0   |

| 7       | 6       | 5       | 4       | 3       | 2       | 1      | 0      |

| 保留      | IRQ0.6  | IRQ0.5  | IRQ0.4  | IRQ0.3  | IRQ0.2  | IRQ0.1 | IRQ0.0 |

| RW 0    | RW 0   | RW 0   |

注:

1) 写入 1 会发出一个中断请求到 DSP 内核,写入 0 无影响。

2) 有中断请求而未被响应, 称为挂起。

|        | IRQ0.0~IRQ0.15: |

|--------|-----------------|

| 位 15~0 | 0: 未挂起中断请求      |

|        | 1:挂起中断请求        |

### 外设中断请求寄存器 PIRQRO 各位的定义

| 位的位置    | 中断      | 中断描述             | 中断优先级 |

|---------|---------|------------------|-------|

| IRQ0.0  | PDPINTA | 功率驱动保护引脚中断       | INT1  |

| IRQ0.1  | ADCINT  | 高优先级模式 ADC 中断    | INT1  |

| IRQ0.2  | XINT1   | 高优先级模式的外部引脚 1 中断 | INT1  |

| IRQ0.3  | XINT2   | 高优先级模式的外部引脚 2 中断 | INT1  |

| IRQ0.4  | SPIINT  | 高优先级模式的 SPI 中断   | INT1  |

| IRQ0.5  | RXINT   | 高优先级模式的 SCI 接收中断 | INT1  |

| IRQ0.6  | TXINT   | 高优先级模式的 SCI 发送中断 | INT1  |

| 保留      |         |                  |       |

| 保留      |         |                  |       |

| IRQ0.9  | CMP1INT | Compare1 中断      | INT2  |

| IRQ0.10 | CMP2INT | Compare2 中断      | INT2  |

| IRQ0.11 | CMP3INT | Compare3 中断      | INT2  |

| IRQ0.12 | T1PINT  | Timer1 周期中断      | INT2  |

| IRQ0.13 | T1CINTT | Timer1 比较中断      | INT2  |

| IRQ0.14 | T1UPINT | Timer1 下溢中断      | INT2  |

| IRQ0.15 | T10FINT | Timer1 上溢中断      | INT2  |

### 3.外设中断请求寄存器 PIRQR1—7011h

| 15   | 14      | 13      | 12      | 11      | 10      | 9      | 8      |

|------|---------|---------|---------|---------|---------|--------|--------|

| 保留   | IRQ1.14 | IRQ1.13 | IRQ1.12 | IRQ1.11 | IRQ1.10 | IRQ1.9 | IRQ1.8 |

| RW_0 | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0   | RW_0   |

V1.4

| 7    | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|

| 保留   | IRQ1.6 | IRQ1.5 | IRQ1.4 | IRQ1.3 | IRQ1.2 | IRQ1.1 | IRQ1.0 |

| RW 0 | RW 0   | RW 0   | RW 0   | RW 0   | RW 0   | RW 0   | RW 0   |

注:

1) 写入 1 会发出一个中断请求到 DSP 内核,写入 0 无影响。

2) 有中断请求而未被响应, 称为挂起。

IRQ1.0~IRQ1.15: 0: 未挂起中断请求 位 15~0

1:挂起中断请求

## 外设中断请求寄存器 PIRQR1 各位的定义

| 位的位置    | 中断      | 中断描述             | 中断优先级 |

|---------|---------|------------------|-------|

| IRQ1.0  | T2PINT  | Timer2 周期中断      | INT3  |

| IRQ1.1  | T2CINT  | Timer2 比较中断      | INT3  |

| IRQ1.2  | T2UFINT | Timer2 下溢中断      | INT3  |

| IRQ1.3  | T2OFINT | Timer2 上溢中断      | INT3  |

| IRQ1.4  | CAP1INT | Capture1 中断      | INT4  |

| IRQ1.5  | CAP2INT | Captuer2 中断      | INT4  |

| IRQ1.6  | CAP3INT | Capture3 中断      | INT4  |

| IRQ1.7  | SPIINT  | 低优先级模式的 SPI 中断   | INT5  |

| IRQ1.8  | RXINT   | 低优先级模式的 SCI 接收中断 | INT5  |

| IRQ1.9  | TXINT   | 低优先级模式的 SCI 发送中断 | INT5  |

| 保留      |         |                  |       |

| 保留      |         |                  |       |

| IRQ1.12 | ADCINT  | 低优先级模式的 ADC 中断   | INT6  |

| IRQ1.13 | XINT1   | 低优先级模式的外部引脚 1 中断 | INT6  |

| IRQ1.14 | XINT2   | 低优先级模式的外部引脚 2 中断 | INT6  |

| 保留      |         |                  |       |

#### 4.外设中断请求寄存器 PIRQR2—7012h

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| 保留   |

| RW_0 |

|      |      |      |      |      |      |      |      |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 保留   |

| RW_0 | RW 0 |

注:

1) 写入 1 会发出一个中断请求到 DSP 内核,写入 0 无影响。

2) 有中断请求而未被响应, 称为挂起。

V1.4

IRQ2.0~IRQ2.15:

位 15~0

0 : 未挂起的中断请求 1 : 挂起中断请求

## 5.外设中断应答寄存器 PIACKR0—7014h

|   | 15      | 14      | 13      | 12      | 11      | 10      | 9      | 8      |

|---|---------|---------|---------|---------|---------|---------|--------|--------|

| I | IAK0.15 | IAK0.14 | IAK0.13 | IAK0.12 | IAK0.11 | IAK0.10 | IAK0.9 | 保留     |

|   | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0   | RW_0   |

|   |         |         |         |         |         |         |        |        |

|   | 7       | 6       | 5       | 4       | 3       | 2       | 1      | 0      |

|   | 保留      | IAK0.6  | IAK0.5  | IAK0.4  | IAK0.3  | IAK0.2  | IAK0.1 | IAK0.0 |

|   | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0   | RW_0   |

| 柼 15~0         | IAK0.0~IAK0.15:            |

|----------------|----------------------------|

| <u>  15.40</u> | 外设中断应答位。写 1 到对应的中断应答位可以清零。 |

注:对该寄存器写 1 插入中断应答并不更新 PIVR 寄存器的内容,读此寄存器返回值是 0。

## 外设中断应答寄存器 PIACKRO 各位的定义

| 位的位置    | 中断      | 中断描述             | 中断优先级 |

|---------|---------|------------------|-------|

| IAK0.0  | PDPINTA | 功率驱动保护引脚中断       | INT1  |

| IAK0.1  | ADCINT  | 高优先级模式 ADC 中断    | INT1  |

| IAK0.2  | XINT1   | 高优先级模式的外部引脚 1 中断 | INT1  |

| IAK0.3  | XINT2   | 高优先级模式的外部引脚 2 中断 | INT1  |

| IAK0.4  | SPIINT  | 高优先级模式的 SPI 中断   | INT1  |

| IAK0.5  | RXINT   | 高优先级模式的 SCI 接收中断 | INT1  |

| IAK0.6  | TXINT   | 高优先级模式的 SCI 发送中断 | INT1  |

| 保留      |         |                  |       |

| 保留      |         |                  |       |

| IAK0.9  | CMP1INT | Compare1 中断      | INT2  |

| IAK0.10 | CMP2INT | Compare2 中断      | INT2  |

| IAK0.11 | CMP3INT | Compare3 中断      | INT2  |

| IAK0.12 | T1PINT  | Timer1 周期中断      | INT2  |

| IAK0.13 | T1CINTT | Timer1 比较中断      | INT2  |

| IAK0.14 | T1UPINT | Timer1 下溢中断      | INT2  |

| IAK0.15 | T10FINT | Timer1 上溢中断      | INT2  |

## 6.外设中断应答寄存器 PIACKR1—7015h

|   | 15   | 14      | 13      | 12      | 11      | 10      | 9      | 8      |

|---|------|---------|---------|---------|---------|---------|--------|--------|

|   | 保留   | IAK1.14 | IAK1.13 | IAK1.12 | IAK1.11 | IAK1.10 | IAK1.9 | IAK1.8 |

| • | RW_0 | RW_0    | RW_0    | RW_0    | RW_0    | RW_0    | RW_0   | RW_0   |

|   |      |         |         |         |         |         |        |        |

|   | 7    | 6       | 5       | 4       | 3       | 2       | 1      | 0      |

|   | 保留   | IAK1.6  | IAK1.5  | IAK1.4  | IAK1.3  | IAK1.2  | IAK1.1 | IAK1.0 |

|   | RW 0 | RW 0    | RW 0    | RW 0    | RW 0    | RW 0    | RW 0   | RW 0   |

IAK1.0~IAK1.15: 位 15~0 外设中断应答位。写1到对应的中断应答位可以清除此位。

注:对该寄存器写 1 插入中断应答并不更新 PIVR 寄存器的内容,读此寄存器返回值是 0。

# 外设中断应答寄存器 PIACKR1 各位的定义

| 位的位置    | 中断      | 中断描述             | 中断优先级 |

|---------|---------|------------------|-------|

| IAK1.0  | T2PINT  | Timer2 周期中断      | INT3  |

| IAK1.1  | T2CINT  | Timer2 比较中断      | INT3  |

| IAK1.2  | T2UFINT | Timer2 下溢中断      | INT3  |

| IAK1.3  | T2OFINT | Timer2 上溢中断      | INT3  |

| IAK1.4  | CAP1INT | Capture1 中断      | INT4  |

| IAK1.5  | CAP2INT | Captuer2 中断      | INT4  |

| IAK1.6  | CAP3INT | Capture3 中断      | INT4  |

| IAK1.7  | SPIINT  | 低优先级模式的 SPI 中断   | INT5  |

| IAK1.8  | RXINT   | 低优先级模式的 SCI 接收中断 | INT5  |

| IAK1.9  | TXINT   | 低优先级模式的 SCI 发送中断 | INT5  |

| 保留      |         |                  |       |

| 保留      |         |                  |       |

| IAK1.12 | ADCINT  | 低优先级模式的 ADC 中断   | INT6  |

| IAK1.13 | XINT1   | 低优先级模式的外部引脚 1 中断 | INT6  |

| IAK1.14 | XINT2   | 低优先级模式的外部引脚 2 中断 | INT6  |

| 保留      |         |                  |       |

#### 7.外设中断应答寄存器 PIACKR2—7016h

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| 保留   |

| RW_0 |

|      |      |      |      |      |      |      |      |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 保留   |

| RW_0 |

| ☆ 15~0 | IAK2.0~IAK2.15:              |

|--------|------------------------------|

|        | 外设中断应答位。写 1 到对应的中断应答位可以清除此位。 |

注:对该寄存器写 1 插入中断应答并不更新 PIVR 寄存器的内容,读此寄存器返回值是 0。

# 9.4 外设中断控制寄存器

该系列器件包含两个外部中断控制寄存器 XINT1CR 和 XINT2CR,用于控制和监控 XINT1 和 XINT2 的引脚状态。

#### 1.外部中断寄存器 XINT1CR—7070h

| 15         | 14~3 | 2              | 1              | 0            |

|------------|------|----------------|----------------|--------------|

| XINT1 flag | 保留位  | XINT1 polarity | XINT1 priority | XINT1 enable |

| RC_0       | R_0  | RW_0           | RW-0           | RW_0         |

注: R=可读, W=可写, C=清除, \_0=复位值, S=只可被置位;

| 位 15   | XINT1 flag:该位指示在 XINT1 引脚上是否检测到一个所选的跳变。无论外部中断 1 是否被使能,该位都可置位。当相应的中断被应答,该位被自动清 0。通过软件向该位写 1 (写 0 无效)或者器件复位时,该位也被清 0。 |

|--------|---------------------------------------------------------------------------------------------------------------------|

|        | 0 : 未检测到跳变;                                                                                                         |

|        | 1 : 检测到跳变;                                                                                                          |

| 位 14~3 | 保留位                                                                                                                 |

|        | XINT1 polarity; XINT1 极性,该位决定中断触发来自上升沿还是下降沿;                                                                        |

| 位 2    | 0 : 在下降沿产生中断 (由高到低跳变) ;                                                                                             |

|        | 1 : 在上升沿产生中断(由低到高跳变);                                                                                               |

|        | XINT1 priority:XINT1 优先级,该读/写位决定哪一个中断优先级被请求,CPU 的优先                                                                 |

|        | 级层次和相应的高低优先级已经被编码到外设中断扩展寄存器中,可查阅表 9-1 中断源优                                                                          |

| 位 1    | 先级和向量表;                                                                                                             |

|        | 0 : 高优先级;                                                                                                           |

|        | 1 : 低优先级;                                                                                                           |

|        | XINT1 enable:XINT1 使能位,该读写位使能或禁止外部中断 XINT1;                                                                         |

| 位 0    | 0 : 屏蔽中断;                                                                                                           |

|        | 1 : 使能中断;                                                                                                           |

#### 2.外部中断寄存器 XINT2CR—7071h

| 15         | 14~3 | 2              | 1              | 0            |  |

|------------|------|----------------|----------------|--------------|--|

| XINT2 flag | 保留位  | XINT2 polarity | XINT2 priority | XINT2 enable |  |

V1.4

RC\_0

R\_0

RW\_0

RW-0

RW\_0

注: R=可读, W=可写, C=清除, \_0=复位值, S=只可被置位;

| 位 15   | XINT2flag:该位指示在 XINT2 引脚上是否检测到一个所选的跳变。无论外部中断 2 是否被使能,该位都可置位。当相应的中断被应答,该位被自动清 0。通过软件向该位写 1(写 0 无效)或者器件复位时,该位也被清 0。 0 : 未检测到跳变; 1 ; 检测到跳变; |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 位 14~3 | 保留位                                                                                                                                      |

| 位 2    | XINT2 polarity; XINT2 极性,该位决定中断是上升沿产生还是下降沿产生; 0 ; 在下降沿产生中断 (由高到低跳变)产生中断;                                                                 |

| 111 2  | 1 ; 在上升沿产生中断(由低到高跳变)产生中断;                                                                                                                |

| 位 1    | XINT2 priority: XINT2 优先级,该读/写位决定哪一个中断优先级被请求,CPU 的优先级<br>层次和相应的高低优先级已经被编码到外设中断扩展寄存器中,可参加表 9-1 中断源优先级<br>和向量表;<br>0 ; 高优先级;<br>1 ; 低优先级;  |

| 位 0    | XINT2 enable: XINT2 使能位,该读写位使能或禁止外部中断 XINT2;         0 ; 屏蔽中断;         1 ; 使能中断;                                                         |

# 10 看门狗

## 10.1 看门狗模块结构框图

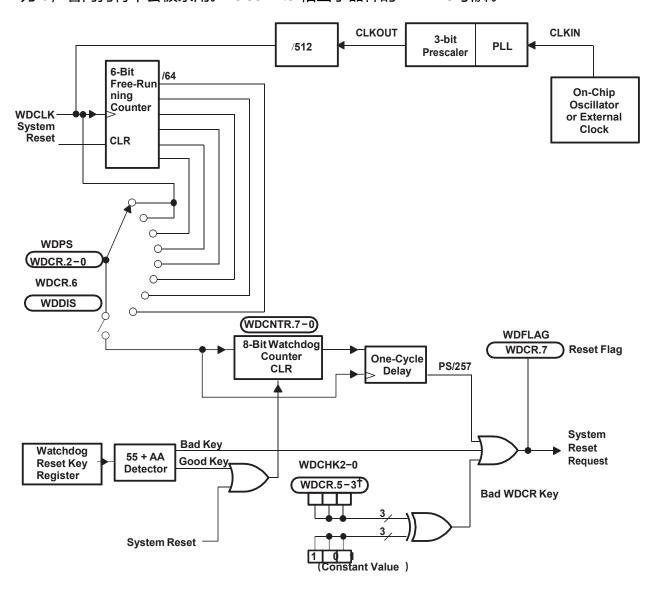

该系列器件集成片内看门狗(Watch Dog)定时器模块。如果器件运行期间没有定 期通过软件写入正确的密钥来监视软、硬件的操作,该模块生成一个系统复位信号。看 门狗定时器独立于 CPU 工作,无需 CPU 初始化。当发生系统复位时,看门狗定时器默 认设置为最高速率(看门狗时钟信号配置为 CLKOUT / 512)。 器件退出复位态, CPU 开始执行代码,看门狗开始递增计数。为了避免器件上电后触发看门狗超时复位,看门 狗的设置应该在上电复位后尽快完成。有关看门狗模块功能结构如图 10.1 所示。看门狗 功能模块主要包括以下部分:

- 看门狗定时器

- 7 种不同看门狗溢出速率

- 一个密钥寄存器(WDKEY),写入正确值清除看门狗计数器,写入错误值触发 系统复位

- 检测对应的控制位, 当写入一个错误值到 WDCR 寄存器, 将触发系统复位

- 一旦系统复位解除,看门狗计数器自动激活

- 三个看门狗控制寄存器。

注: 此模块中的所有寄存器都是8位寄存器,当一个寄存器被访问时,所述寄存器的数 据在低字节,高位字节被读为零。对高位字节写入无效。

表 10.1 列出了不同的看门狗溢出速率配置, 当 SCSR2 寄存器的第 5 位 (SCSR2.5) 为 1 时, WDCR 寄存器的第 6 位 (WDCR.6) 写 "1" 可以禁用看门狗。如果 SCSR2.5 为 0,看门狗将不会被禁用。 SCSR2.5 相当于器件的 WDDIS 引脚。

图 10.1 看门狗功能框图

# 10.2 看门狗控制寄存器

#### 1. 看门狗计数寄存器 WDCNTR—7023h

8 位看门狗计数寄存器存放看门狗当前的计数值,寄存器的 D7~D0 位。WDCNTR 是一个只读寄存器,复位后为 0,对寄存器写入无效。

# 2. 看门狗密钥寄存器 WDKEY—7025h

顺序写入 55h+AAh (复位关键字) 到 WDKEY 时,将复位看门狗计数器的值,其它 写入值的组合或除 55h、AAh 之外写入值都不能清除 WDCNTR;

8 位 WDKEY 是一个可读写寄存器,复位后为 0。读取该寄存器将返回 WDCR 中内 容。

## 3. 看门狗控制寄存器 WDCR—7029h

8位 WDCR 用作存放看门狗配置的控制位。

| 7      | 6     | 5      | 4      | 3      | 2     | 1     | 0     |

|--------|-------|--------|--------|--------|-------|-------|-------|

| WDFLAG | WDDIS | WDCHK2 | WDCHK1 | WDCHK0 | WDPS2 | WDPS1 | WDPS0 |

| RC_x   | RWC_0 | RW_0   | RW_0   | RW_0   | RW_0  | RW_0  | RW_0  |

注: R=可读, W=可写, C=清除, \_0=复位值, \_X=复位值不确定, S=只可被置位;

|           | WDFLAG:看门狗标志位。该位用作判断看门狗定时器是否产生一个看门狗复位。看门狗产         |

|-----------|----------------------------------------------------|

|           | 生的复位事件时此位置 1。                                      |

| 位 7       | 0:表明上次清除该位后,WD 定时器没有产生复位;                          |

|           | 1:表明上次清除该位后,WD 定时器已经产生了复位;                         |

|           | WDDIS;禁止看门狗位。仅当 SCSR2 中的 WDOVERIDE 位为 1 时,向该位写入有效; |

| 位 6       | 0; 使能看门狗;                                          |

|           | 1;禁止看门狗。                                           |

| 0 - 0 -   | WDCHK2~ WDCHK0:看门狗检查位。必须向此三位写 101h,系统才继续正常运行。否则    |

| 位 5 ~ 位 3 | 将触发一个系统复位。读这三位返回 000h;                             |

|           | WDPS1~WDPS0:看门狗预定标因子选择位。这三位选择产生用于WD计数器CLK的计数       |

| 位 2 ~ 位 0 | 溢出分频 (表 9-1 列出了 WD 溢出时间选择,WD 计数器在溢出前计数 257 个时钟,给定最 |

|           | 小溢出时间。)                                            |

# 进版电子 Advancechip ADM16F03A1 Digital Signal Processor

# 表 10. 1 WD 溢出时间选择

| ,     | WD 频选择 BITS | 5     |          | 看门狗时钟速率 f  | 最小溢出时间         |  |

|-------|-------------|-------|----------|------------|----------------|--|

| WDPS2 | WDPS1       | WDPS0 | WDCLK 分频 | 频率 (Hz)    | 时间 (s)         |  |

| 0     | 0           | х     | 1        | WDCLK / 1  | (256*1)/WDCLK  |  |

| 0     | 1           | 0     | 2        | WDCLK / 2  | (256*2)/WDCLK  |  |

| 0     | 1           | 1     | 4        | WDCLK / 4  | (256*4)/WDCLK  |  |

| 1     | 0           | 0     | 8        | WDCLK / 8  | (256*8)/WDCLK  |  |

| 1     | 0           | 1     | 16       | WDCLK / 16 | (256*16)/WDCLK |  |

| 1     | 1           | 0     | 32       | WDCLK / 32 | (256*32)/WDCLK |  |

| 1     | 1           | 1     | 64       | WDCLK / 64 | (256*64)/WDCLK |  |

# 11 硬件加速单元

# 11.1 硬件加速单元功能介绍

硬件加速单元的功能特性描述如下:

(1) 开平方根运算

输入数据为 32bit 的无符号整数,运算结果为 16bit 无符号整数; 硬件运算花销 17 个周期;

(2) 除法运算

被除数和除数皆为 32bit 有符号整数;

实现有符号的整数除法,保留余数,商和余数皆为 32bit 有符号整数;

(3) 乘法移位运算

实现 32bit 有符号整数乘法运算;

硬件运算花销33个周期;

运算结果在无移位操作时为 64bit 的乘法运算结果; 在有移位操作时, 运算结果保留 移位后的低 32bit 数据;

硬件运算花销 17 个周期

(4) park 变换运算

输入变量为 $\alpha$ ,  $\beta$ ,  $\theta$ 三个 16bit 的有符号变量, 输出为 d、q 两个 16bit 有符号数据; 计算公式:

$$d = \cos(\theta) * \alpha + \sin(\theta) * \beta$$

$$q=-\sin (\theta) * \alpha + \cos (\theta) * \beta$$

硬件运算花销74个周期;

(5) 反正切运算

坐标 (x, y) 输入为 16bit 的有符号数据;

坐标原点偏移可调;

坐标预乘系数可调;

输出角度支持两种模式: Q 模式和 N 模式;

硬件运算花销 15 个周期;

- (6) CPU 采用轮询模式读取 FOC 硬件加速单元运算结果;

- (7) 运算单元集成结果溢出检测、运算中断错误检测等功能;

- (8) 各功能模块皆可软复位。

## 11.2 硬件加速单元各模块详细说明

#### 11.2.1 开平方根模块

#### 1. 开平方根模块使用说明

使用 sqrt 运算开启方法是,在使能 sqrt 模块之后,CPU 再更新开方运算输入的 32bit 数据使能运算。

#### 2. 开平方根模块寄存器

(1) 开方运算的输入低 16bit 数据寄存器 r sqrt dl—7512h

16~0

r\_sqrt\_dl

WR CAh

注: R=可读, W=可写, C=清除, \_0=复位值, \_X=复位值不确定, S=只可被置位;

位 16~位0

r\_sqrt\_dl: 开方运算的输入低 16bit 数据寄存器,用来保存开平方模块 32 位输入数据的低 16 位输入;

#### (2) 开方运算的输入高 16bit 数据寄存器 r sqrt dh—7513h

# 进芯电子 Advancechip ADM16F03A1 Digital Signal Processor

V1.4

16~0

$r_sqrt_dh$

$WR_0$

注: R=可读, W=可写, C=清除, \_0=复位值, \_X=复位值不确定, S=只可被置位;

| 位 16~位 0 | r_sqrt_dh: 开方运算的输入高 16bit 数据寄存器,用来保存开平方模块 32 位输入数据的高 16 位输 |

|----------|------------------------------------------------------------|

| <u> </u> | λ;                                                         |

## (3) 开方运算控制寄存器 r\_sqrt\_ctrl—7514h

| 15~3 | 2          | 1           | 0        |

|------|------------|-------------|----------|

| 保留   | soft reset | sqrt_cal_en | r_st_clr |

| WR 0 | WR 1       | WR 1        | WR 0     |

注: R=可读, W=可写, C=清除, \_0=复位值, \_X=复位值不确定, S=只可被置位;

| 位 15~位 3 | 保留                                            |

|----------|-----------------------------------------------|

| 位 2      | soft reset:开方模块复位信号,低电平有效(写入 0 复位);           |

|          | Sqrt_cal_en: 开方运算使能位;                         |

| 位 1      | 0: 禁止开方运算模块                                   |

|          | 1: 使能开方运算模块                                   |

| 位 0      | r_st_clr:状态寄存器 r_sqrt_st 清除信号,高电平有效(写入 1 清除); |

#### (4) 开方模块状态寄存器 r\_sqrt\_s—7515h

| 15~4 | 3          | 2           | 1         | 0          |

|------|------------|-------------|-----------|------------|

| 保留位  | r_sqrt_rdy | r_sqrt_busy | r_sqrt_of | r_sqrt_err |

| R_0  | R_0        | R_0         | R_0       | R_0        |

注: R=可读, W=可写, C=清除, \_0=复位值, \_X=复位值不确定, S=只可被置位;

| 位 15~4         | 保留                                 |

|----------------|------------------------------------|

|                | r_sqrt_rdy:运算结束并等待 CPU 获取运算结果的标志位; |

| 位 3            | 0: 标志被复位                           |

|                | 1: 标志被置位                           |

| / <del>-</del> | r_sqrt_busy: 运算处于忙状态的标志位;          |

| 位 2            | 0: 标志被复位                           |

|     | 1: 标志被置位              |

|-----|-----------------------|

|     | r_sqrt_of:运算结果溢出标志位;  |

| 位 1 | 0: 标志被复位              |

|     | 1: 标志被置位              |